Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 114

114

8266A-MCU Wireless-12/09

ATmega128RFA1

Register Bits

Value

Description

2

Antenna 0: DIG1=L, DIG2=H

3

Default value for ANT_EXT_SW_EN=0;

Mandatory setting for applications not using

Antenna Diversity

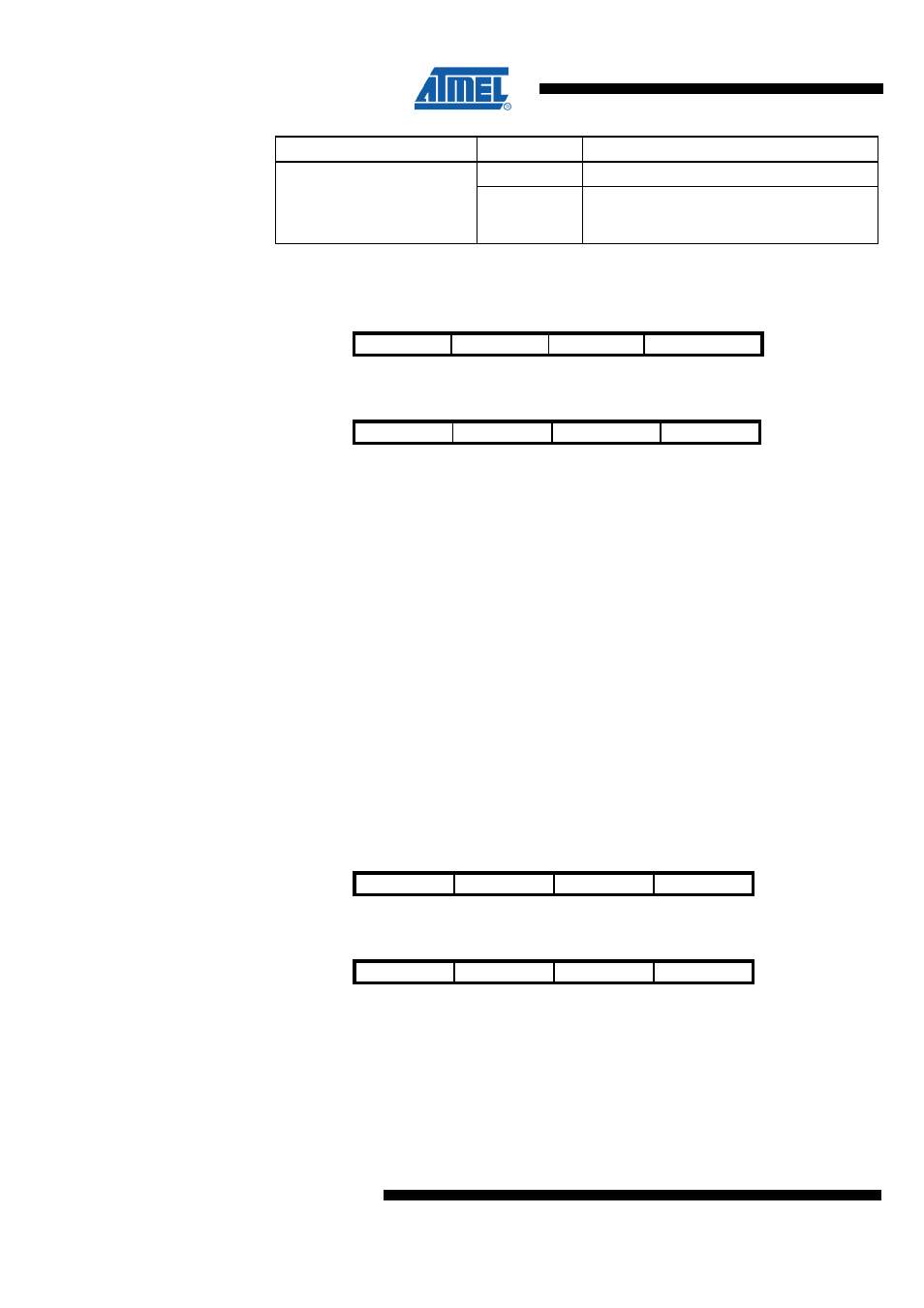

9.12.18 IRQ_MASK – Transceiver Interrupt Enable Register

Bit

7

6

5

4

NA ($14E)

AWAKE_EN

TX_END_EN

AMI_EN

CCA_ED_DONE_EN

IRQ_MASK

Read/Write

RW

RW

RW

RW

Initial Value

0

0

0

0

Bit

3

2

1

0

NA ($14E)

RX_END_EN

RX_START_EN PLL_UNLOCK_EN PLL_LOCK_EN

IRQ_MASK

Read/Write

RW

RW

RW

RW

Initial Value

0

0

0

0

This register is used to enable or disable individual interrupts of the radio transceiver.

An interrupt is enabled if the corresponding bit is set to 1. All interrupts are disabled

after the power up sequence or reset. If an interrupt is enabled it is recommended to

read the interrupt status register IRQ_STATUS first to clear the history.

•

Bit 7 – AWAKE_EN - Awake Interrupt Enable

•

Bit 6 – TX_END_EN - TX_END Interrupt Enable

•

Bit 5 – AMI_EN - Address Match Interrupt Enable

•

Bit 4 – CCA_ED_DONE_EN - End of ED Measurement Interrupt Enable

•

Bit 3 – RX_END_EN - RX_END Interrupt Enable

•

Bit 2 – RX_START_EN - RX_START Interrupt Enable

•

Bit 1 – PLL_UNLOCK_EN - PLL Unlock Interrupt Enable

•

Bit 0 – PLL_LOCK_EN - PLL Lock Interrupt Enable

9.12.19 IRQ_STATUS – Transceiver Interrupt Status Register

Bit

7

6

5

4

NA ($14F)

AWAKE

TX_END

AMI

CCA_ED_DONE

IRQ_STATUS

Read/Write

RW

RW

RW

RW

Initial Value

0

0

0

0

Bit

3

2

1

0

NA ($14F)

RX_END

RX_START

PLL_UNLOCK

PLL_LOCK

IRQ_STATUS

Read/Write

RW

RW

RW

RW

Initial Value

0

0

0

0

This register contains the status of the pending interrupt requests. An interrupt is

pending if the associated bit has a value of one. Such a pending interrupts can be

manually cleared by writing a 1 to that register bit. Interrupts are automatically cleared

when the corresponding interrupt service routine is being executed.

•

Bit 7 – AWAKE - Awake Interrupt Status