2 sram with data retention, 3 voltage regulators (avreg, dvreg), Sram with data retention" on – Rainbow Electronics ATmega128RFA1 User Manual

Page 163: Atmega128rfa1

163

8266A-MCU Wireless-12/09

ATmega128RFA1

AVR State

Radio Transceiver State

Powerchain

off

(2,3)

DEEP SLEEP

off (SLEEP or power reduction)

off

(7)

Notes:

1. Idle

2. Power Down

3. Power Save

4. ADC Noise Reduction Mode

5. Standby

6. Extended Standby

7.

12.5.2 SRAM with Data Retention

It is necessary to prevent any data loss of the SRAM when setting the CPU in one of

the sleep modes. For that purpose the SRAM blocks will not be completely switched off

if the power-chain is disabled. Instead the supply voltage for any individual SRAM block

is decreased to reduce its leakage current but guaranteeing its data retention.

The SRAM memory is divided into four separate blocks. Each block can be fully

switched off by setting the correspondent bit (PRRAM0 ... PRRAM3) in register PRR2

(see

"PRR2 – Power Reduction Register 2" on page 168

). This enables the application

software to switch off unused SRAM memory to save power and to reduce leakage

currents.

Every SRAM block can be enabled again by resetting the respective bit (PRRAM0 ...

PRRAM3) of register PRR2. For each SRAM block n the bit DRTSWOK of the

corresponding register DRTRAMn shows the state of the DRT switch (logic high means

SRAM block can be accessed).

If the power-chain is switched off during deep-sleep modes, the content of the SRAM

blocks must be sustained. To provide data retention and lowest leakage current, a data

retention block controls the SRAM behavior during deep-sleep. Since the leakage

current is dramatically depending from the voltage of the SRAM, the supply voltage can

be decreased by enabling the data retention mode DRT.

Every SRAM block n is controlled by its assigned register DRTRAMn. The bit ENDRT

enables the data retention mode during deep-sleep. If this bit is zero, the respective

SRAM block is completely switched off.

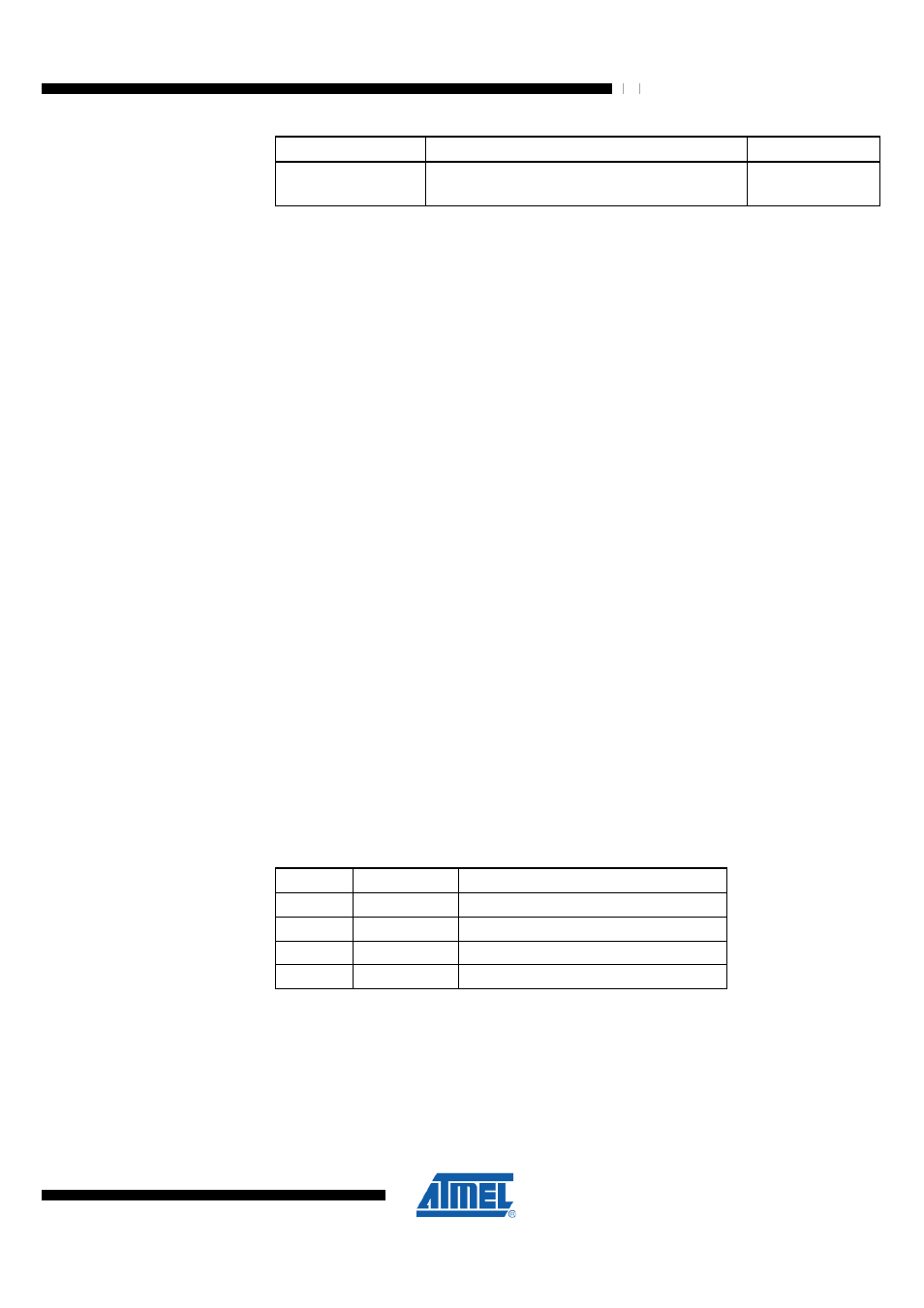

Table 12-3. SRAM behavior while in deep-sleep mode

ENDRT

Power-chain

SRAM supply voltage

1

ON

1.8V (DVDD)

0

ON

1.8V (DVDD)

1

off

Reduced

0

off

Disconnected

The lower 4-bit of the register DRTRAMn are reserved and should not be changed. The

reset value of the DRT voltage settings are preprogrammed during the manufacturing

process and need not to be changed.

12.5.3 Voltage Regulators (AVREG, DVREG)

The main features of the Voltage Regulator blocks are:

•

Bandgap stabilized 1.8V supply for analog and digital domain;