Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 261

261

8266A-MCU Wireless-12/09

ATmega128RFA1

up-counting, and set on the compare match while down-counting. In inverting Output

Compare mode, the operation is inverted. The dual-slope operation has a lower

maximum operation frequency than single slope operation. However these modes are

preferred for motor control applications due to the symmetric feature of the dual-slope

PWM modes.

The PWM resolution for the phase correct PWM mode can be fixed to 8, 9 or 10 bit, or

be defined by either ICRn or OCRnA. The minimum resolution allowed is 2 bit (ICRn or

OCRnA set to 0x0003), and the maximum resolution is 16-bit (ICRn or OCRnA set to

MAX). The PWM resolution R

PCPWM

in bits can be calculated with the following equation:

)

2

log(

)

1

log(

+

=

TOP

R

PCPWM

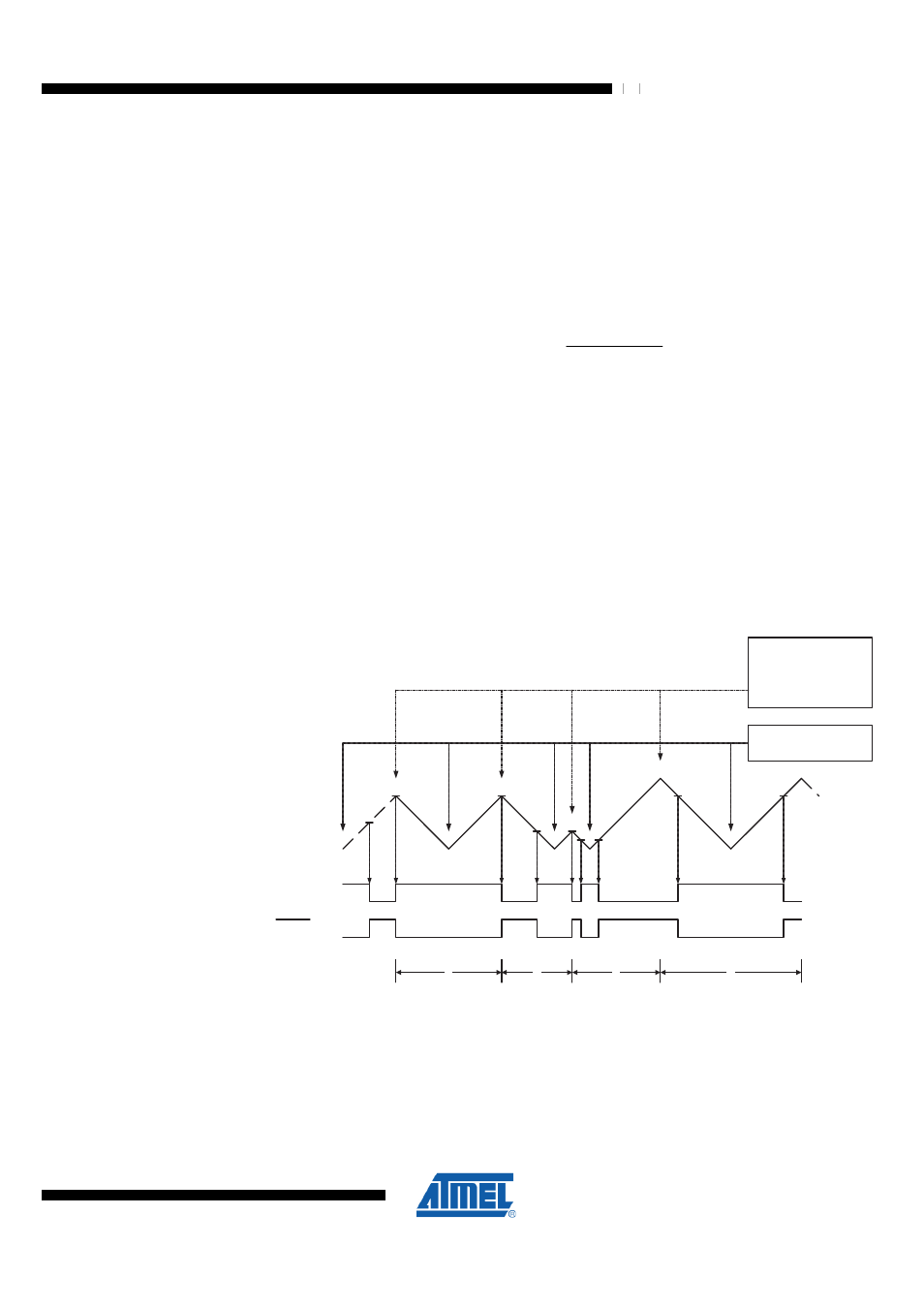

In phase correct PWM mode the counter is incremented until the counter value matches

either one of the fixed values 0x00FF, 0x01FF or 0x03FF (WGMn3:0 = 1, 2, or 3), the

value in ICRn (WGMn3:0 = 10) or the value in OCRnA (WGMn3:0 = 11). The counter

has then reached the TOP and changes the count direction. The TCNTn value will be

equal to TOP for one timer clock cycle. The timing diagram for the phase correct PWM

mode is shown on

. The figure shows phase correct PWM mode

when OCRnA or ICRn is used to define TOP. The TCNTn value is shown in the timing

diagram as a histogram illustrating the dual-slope operation. The diagram includes non-

inverted and inverted PWM outputs. The small horizontal line marks on the TCNTn

slopes represent compare matches between OCRnx and TCNTn. The OCnx Interrupt

Flag will be set when a compare match occurs.

Figure 18-8. Phase Correct PWM Mode Timing Diagram

OCRnx/TOP Update and

OCnA Interrupt Flag Set

or ICFn Interrupt Flag Set

(Interrupt on TOP)

1

2

3

4

TOVn Interrupt Flag Set

(Interrupt on Bottom)

TCNTn

Period

OCnx

OCnx

(COMnx1:0 = 2)

(COMnx1:0 = 3)

The Timer/Counter Overflow Flag (TOVn) is set each time the counter reaches

BOTTOM. When either OCRnA or ICRn is used for defining the TOP value, the OCnA

or ICFn Flag is set accordingly at the same timer clock cycle as the OCRnx Registers

are updated with the double buffer value (at TOP). The Interrupt Flags can be used to

generate an interrupt each time the counter reaches the TOP or BOTTOM value.

When changing the TOP value the program must ensure that the new TOP value is

higher or equal to the value of all of the Compare Registers. If the TOP value is lower

than any of the Compare Registers, a compare match will never occur between the