2 interrupt logic, 1 overview, Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 33

33

8266A-MCU Wireless-12/09

ATmega128RFA1

A second configuration bit (SLPTR) is used to control frame transmission or sleep and

wakeup of the transceiver. This bit is not cleared automatically.

The function of the SLPTR bit relates to the current state of the transceiver module and

is summarized in

. The radio transceiver states are explained in detail in

section

.

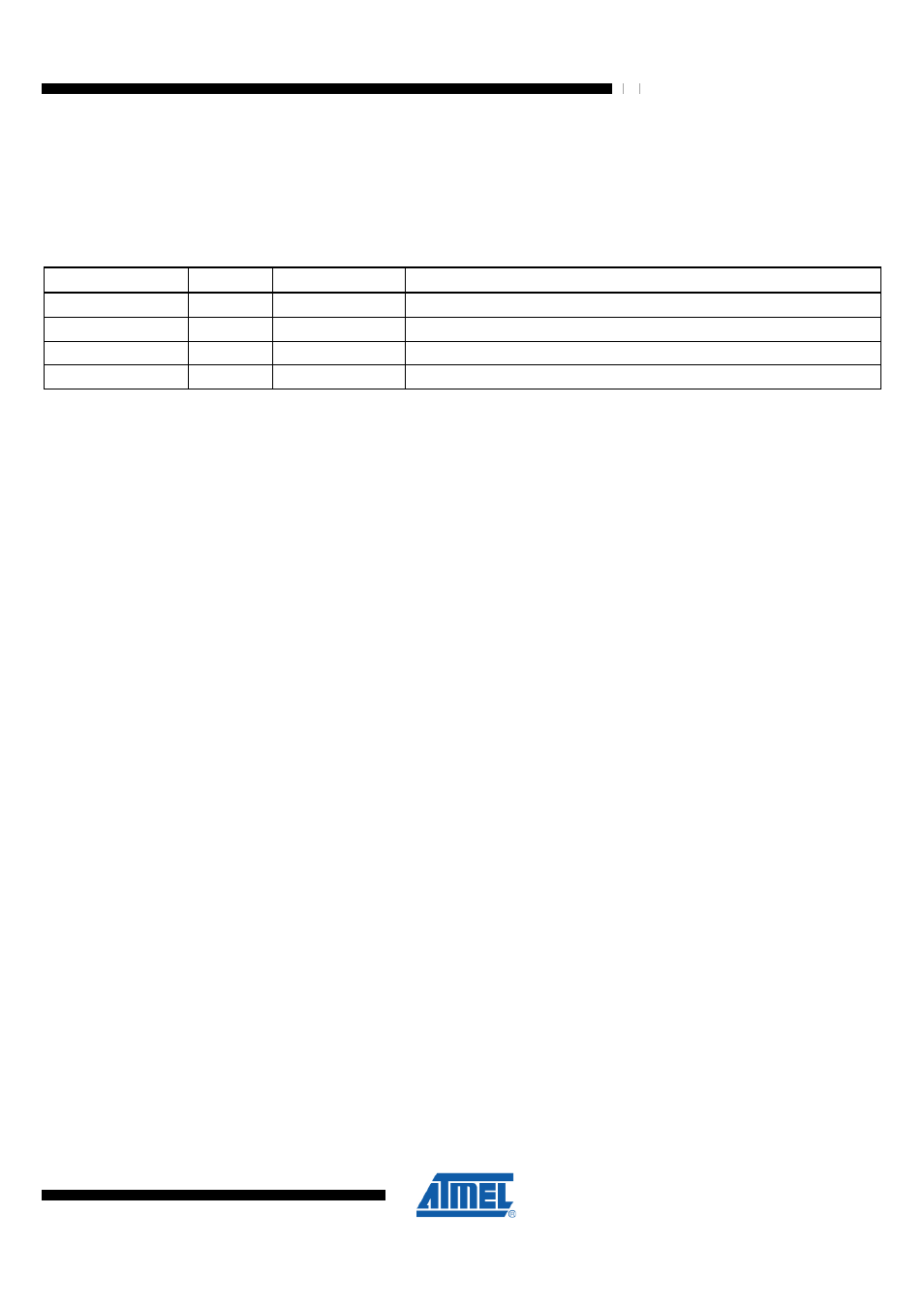

Table 9-1. SLPTR Multi-functional Configuration bit

Transceiver Status

Function

SLPTR Bit

Description

PLL_ON

TX start

“0” “1”

Starts frame transmission

TX_ARET_ON

TX start

“0” “1”

Starts TX_ARET transaction

TRX_OFF

Sleep

“0” “1”

Takes the radio transceiver into SLEEP state

SLEEP

Wakeup

“1” “0”

Takes the radio transceiver back into TRX_OFF state;

In states PLL_ON and TX_ARET_ON, bit SLPTR is used to initiate a TX transaction.

Here bit SLPTR is sensitive on the transition from “0” to “1” only. The bit should be

cleared before the frame transmission is finished.

After initiating a state change by a “0” to “1” transition at bit SLPTR in radio transceiver

states TRX_OFF, RX_ON or RX_AACK_ON, the radio transceiver remains in the new

state as long as the bit is logical “1” and returns to the preceding state if the bit is set to

“0”.

SLEEP state

The SLEEP state is used when radio transceiver functionality is not required, and thus

the receiver module can be powered down to reduce the overall power consumption.

When the radio transceiver is in TRX_OFF state the microcontroller forces the

transceiver to SLEEP by setting SLPTR = “1”. The transceiver awakes when the

microcontroller releases bit SLPTR.

9.3.2 Interrupt Logic

9.3.2.1 Overview

The transceiver module differentiates between eight interrupt events. Internally all

pending interrupt are stored in a separate bit of the interrupt status register

(IRQ_STATUS). Each interrupt is enabled by setting the corresponding bit in the

interrupt mask register (IRQ_MASK). If an IRQ is enabled an interrupt service routine

must be defined to handle the IRQ. A pending IRQ is cleared automatically if an

Interrupt service routine is called. It is also possible to handle IRQs manually by polling

the IRQ_STATUS register. If an IRQ occurred, the appropriate IRQ_STATUS register

bit is set. The IRQ can be cleared by writing ‘1’ to the register bit. It is recommended to

clear the corresponding status bit before enabling an interrupt.

Interrupts are not cleared automatically when the event that caused them vanishes.

More information about interrupt handling by the controller can be found in section

.

The supported interrupts for the Basic Operating Mode are summarized in