12 power management and sleep modes, 1 deep-sleep mode, 2 avr microcontroller sleep modes – Rainbow Electronics ATmega128RFA1 User Manual

Page 156: Power management and sleep modes, Atmega128rfa1

156

8266A-MCU Wireless-12/09

ATmega128RFA1

12 Power Management and Sleep Modes

Sleep modes enable the application to shut down unused modules in the MCU, thereby

saving power. The AVR microcontroller and the RF transceiver provide various sleep

modes allowing the user to tailor the power consumption to the application’s

requirements.

12.1 Deep-Sleep Mode

When the microcontroller goes into Power-down or Power-save modes while the

transceiver is in SLEEP state the device enters the Deep-Sleep mode.

Sending the microcontroller to Power-down or Power-save is not allowed during the

wake-up phase of the transceiver. The TRX24_AWAKE interrupt shall be used to wait

for the transceiver is operational.

The DVDD voltage regulator and the associated power chain will be switched off.

Remaining running logic will then be supplied from the Low Leakage Voltage Regulator.

Even the AVDD regulator will switched off. See chapter

how to disable the radio transceiver.

The SRAM blocks use the data retention mode to preserve its content while saving

leakage power. The Low Leakage Voltage Regulator has only limited driving

capabilities, see section

"Supply Voltage and Leakage Control" on page 161

for details.

Therefore the remaining running logic must be clocked with low frequencies only.

The Deep-Sleep mode can be finished by a wake-up source shown by the

. Then DVDD voltage regulator and the associated power chain will be switched

on. If the power-chain is completely enabled the standard AVR wake-up procedure

continues (for details see chapter

).

Note that the wake-up time from Deep-sleep mode is significantly longer than the wake-

up time from the Power-down or Power-save mode because the entire power-chain will

be restarted.

Additionally note that if the ADC is enabled and/or running a conversion, while entering

Deep-sleep mode, the ADC supply voltage is switched off. Therefore the ADC must be

disabled before entering Deep-sleep mode to avoid an undefined ADC operation.

12.2 AVR Microcontroller Sleep Modes

"System Clock and Clock Options" on page 147

the different clock systems

in the ATmega128RFA1, and their distribution were presented.

is helpful in selecting an appropriate sleep mode. The following table shows the

different sleep modes and their wake-up sources.

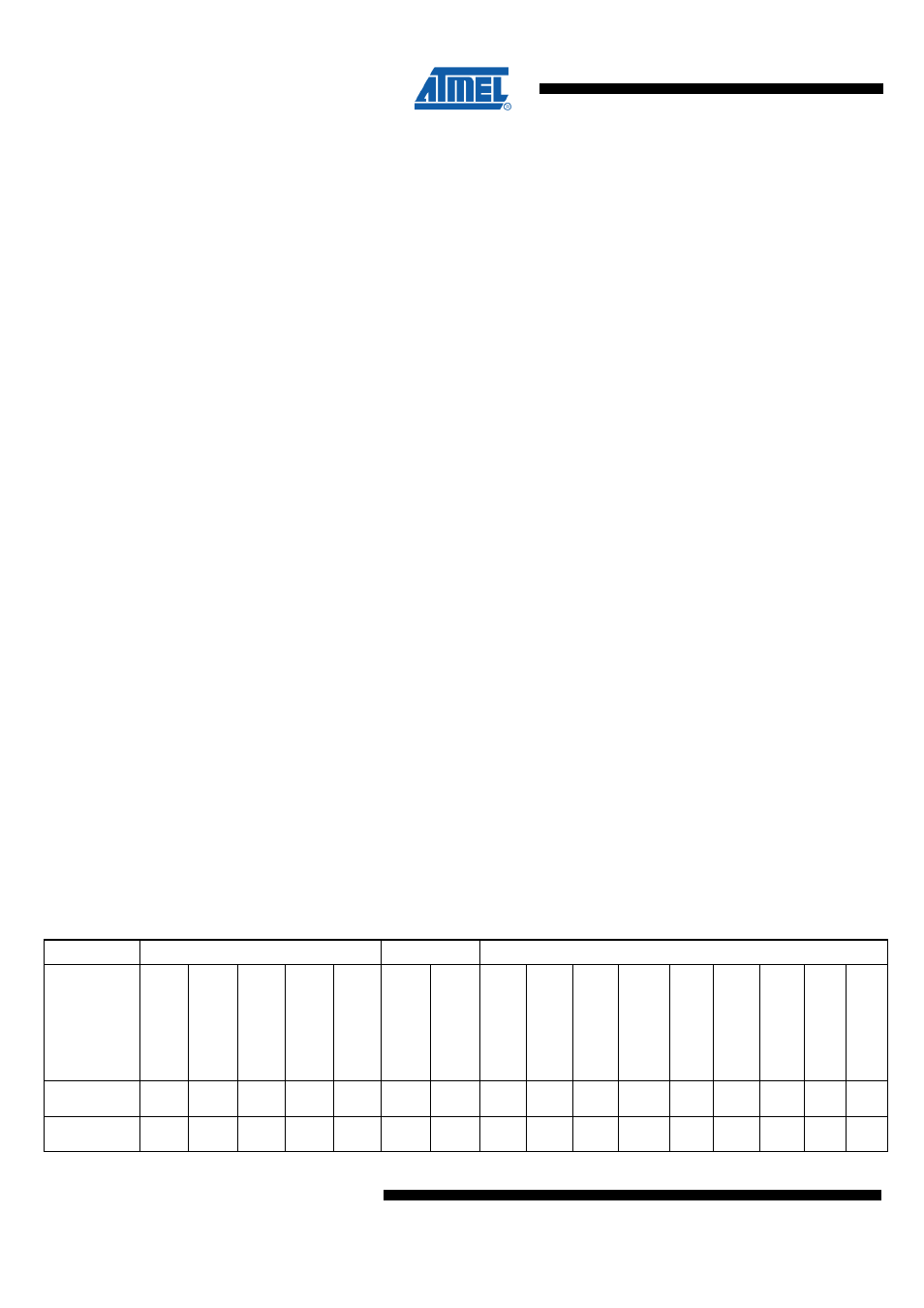

Table 12-1. Active Clock Domains and Wake-up Sources in the Different Sleep Modes

Active Clock Domains

Oscillators

Wake-up Sources

Sleep Mode

c

lk

C

P

U

c

lk

F

L

A

S

H

c

lk

IO

c

lk

A

D

C

c

lk

A

S

Y

M

a

in

C

lo

c

k

-

s

o

u

rc

e

E

n

a

b

le

d

T

im

e

r

O

s

c

il

la

to

r

E

n

a

b

le

d

IN

T

7

:0

a

n

d

P

in

C

h

a

n

g

e

T

W

I

A

d

d

re

s

s

M

a

tc

h

T

im

e

r/

C

o

u

n

te

r2

S

P

M

/E

E

P

R

O

M

R

e

a

d

y

A

D

C

W

D

T

I

n

te

rr

u

p

t

O

th

e

r

I/

O

S

y

m

b

o

l

C

o

u

n

te

r

T

ra

n

s

c

e

iv

e

r

Idle

X

X

X

X

X

(2)

X

X

X

X

X

X

X

X

X

ADCNRM

X

X

X

X

(2)

X

(3)

X

X

(2)

X

X

X

X

X