3 twsr - twi status register, Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 403

403

8266A-MCU Wireless-12/09

ATmega128RFA1

pins enabling the slew-rate limiters and spike filters. If this bit is written to zero, the TWI

is switched off and all TWI transmissions are terminated regardless of any ongoing

operation.

•

Bit 1 – Res - Reserved Bit

This bit is reserved for future use. A read access always will return zero. A write access

does not modify the content.

•

Bit 0 – TWIE - TWI Interrupt Enable

When this bit is written to one and the I-bit in SREG is set, the TWI interrupt request will

be activated for as long as the TWINT Flag is high.

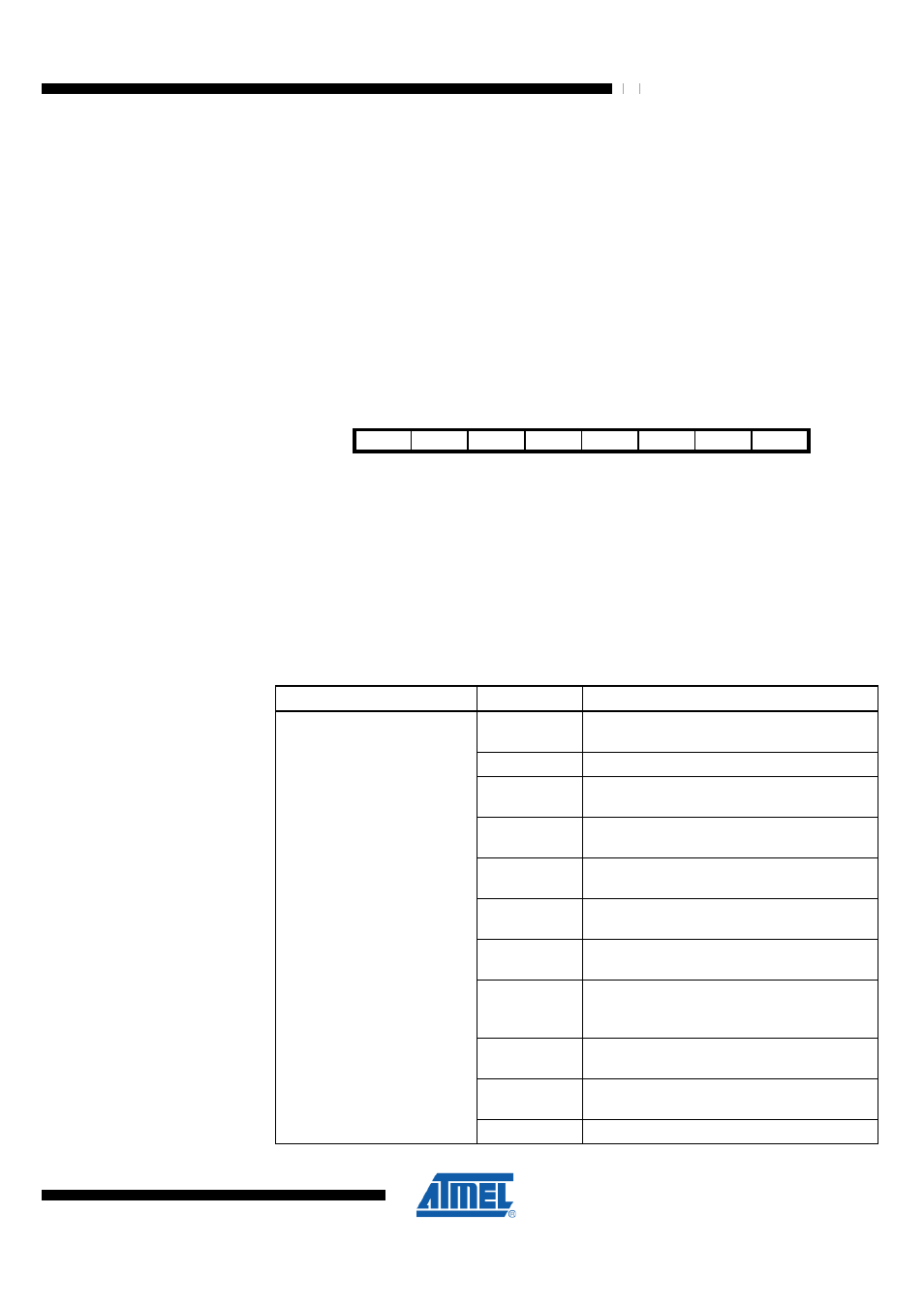

25.9.3 TWSR – TWI Status Register

Bit

7

6

5

4

3

2

1

0

NA ($B9)

TWS7

TWS6

TWS5

TWS4

TWS3

Res

TWPS1

TWPS0

TWSR

Read/Write

RW

RW

RW

RW

RW

R

RW

RW

Initial Value

0

0

0

0

0

0

0

0

•

Bit 7:3 – TWS4:0 - TWI Status

These 5 bits reflect the status of the TWI logic and the 2-wire Serial Bus. The different

status codes for both transmitter and receiver mode are described in the following table.

Note that the value read from TWSR contains both the 5-bit status value and the 2-bit

prescaler value. The application designer should mask the prescaler bits to zero when

checking the Status bits. This makes status checking independent of prescaler setting.

This approach is used in this datasheet, unless otherwise noted.

Table 25-8 TWS Register Bits

Register Bits

Value

Description

0x00

Bus error due to illegal START or STOP

condition.

0x08

A START condition has been transmitted.

0x10

A repeated START condition has been

transmitted.

0x18

SLA+W has been transmitted; ACK has

been received.

0x20

SLA+W has been transmitted; NOT ACK has

been received.

0x28

Data byte has been transmitted; ACK has

been received.

0x30

Data byte has been transmitted; NOT ACK

has been received.

0x38

Arbitration lost in SLA+W or data bytes

(Transmitter); Arbitration lost in SLA+R or

NOT ACK bit (Receiver).

0x40

SLA+R has been transmitted; ACK has been

received.

0x48

SLA+R has been transmitted; NOT ACK has

been received.

TWS4:0

0x50

Data byte has been received; ACK has been