4 low leakage voltage regulator (llvreg) – Rainbow Electronics ATmega128RFA1 User Manual

Page 164

164

8266A-MCU Wireless-12/09

ATmega128RFA1

•

Low dropout (LDO) voltage regulator;

•

Configurable to use an external voltage regulator;

The internal voltage regulators supply a stabilized voltage to the ATmega128RFA1. The

AVREG provides the regulated 1.8V supply voltage for the analog section and the

DVREG supplies the 1.8V supply voltage for the digital section. The DVREG is enabled

during startup and is switched off if the power-chain is disabled. The AVREG is enabled

only on request by either the A/D converter or the radio transceiver.

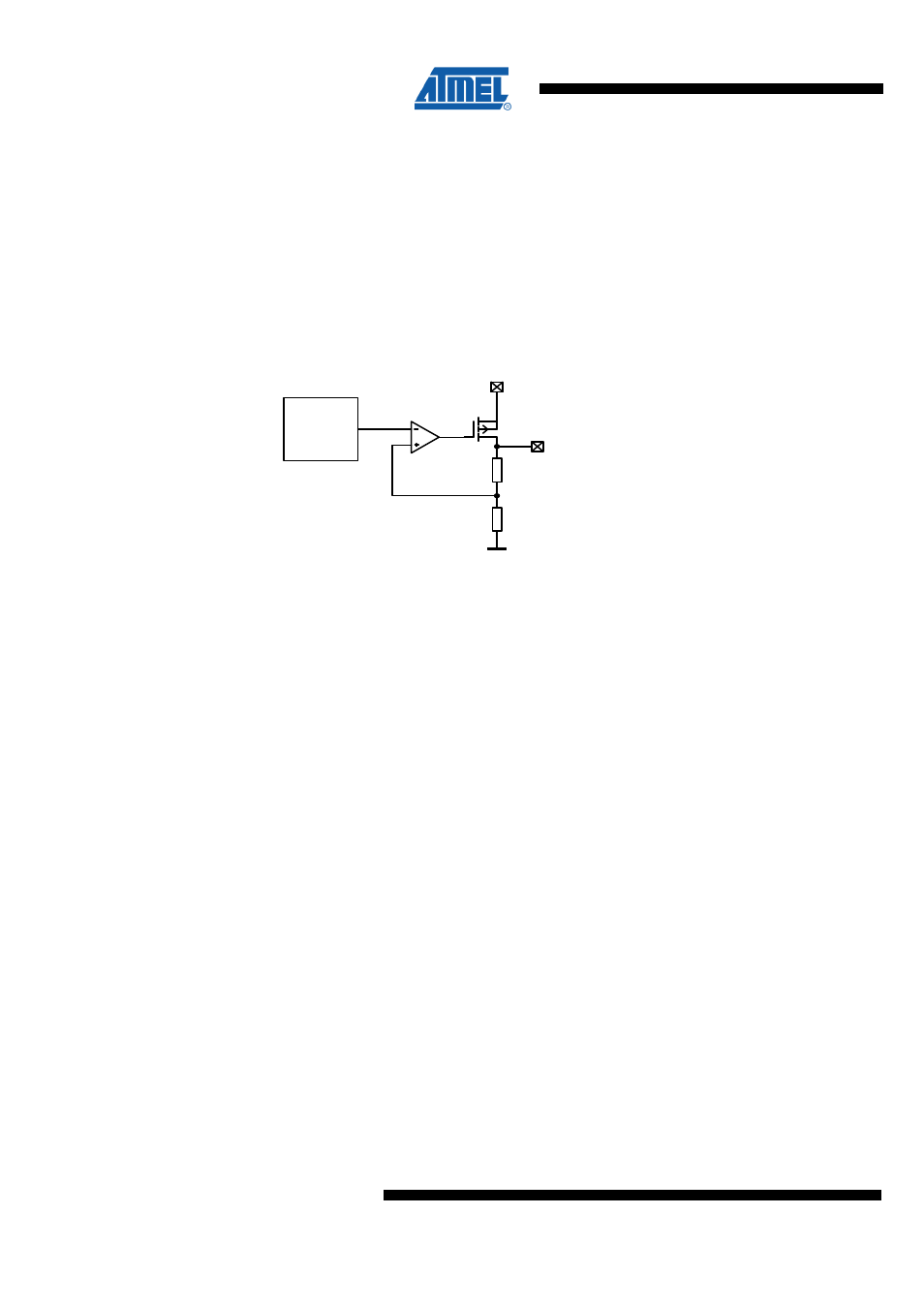

A simplified schematic of the internal voltage regulator is shown in

.

Figure 12-4. Simplified Schematic of AVREG/DVREG

B andgap

voltage

reference

1 .25 V

A V D D ,

D V D D

(D )E V D D

The voltage regulators require bypass capacitors for stable operation. The value of the

bypass capacitors determines their settling time. The bypass capacitors shall be placed

as close as possible to the pins and shall be connected to ground with the shortest

possible traces.

The voltage regulators can be configured with the register VREG_CTRL. It is

recommended to use the internal regulators but it is also possible to supply the low

voltage domains by an external voltage supply. For this configuration the internal

regulators need to be switched off by setting the register bits to the values

AVREG_EXT = 1 and DVREG_EXT = 1 (see

"VREG_CTRL – Voltage Regulator

Control and Status Register" on page 115

). A regulated external supply voltage of 1.8V

must then be connected to the pins 13, 14 (DVDD) and pin 29 (AVDD). When turning

on the external supply ensure a sufficiently long stabilization time before interacting with

the ATmega128RFA1.

The status bits AVDD_OK = 1 and DVDD_OK = 1 of register VREG_CTRL indicate an

enabled and stable internal supply voltage. Reading value 0 indicates that the internal

supply voltage is disabled or not yet settled to the final value.

Note that disabling the digital voltage regulator by DVREG_EXT bit is for internal use

only.

12.5.4 Low Leakage Voltage Regulator (LLVREG)

The main digital voltage regulator (DVREG) will be switched off during the deep sleep

modes “power-down” and “power-save”. The Low Leakage Voltage Regulator will then

keep the digital supply voltage to provide data retention. No application software control

is required.

During the active power states, when the main voltage regulator supplies the chip, the

Low Leakage Voltage Regulator is digitally calibrated. Its output voltage is adjusted to

match the output voltage of the main regulator. This fixed calibration result is stored and

used when the chip enters a power-down state where the main regulator is switched off.