2 prr0 - power reduction register0, Prr0 – power reduction register0" on, Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 167

167

8266A-MCU Wireless-12/09

ATmega128RFA1

The SE bit must be written to logic one to make the MCU enter the sleep mode when

the SLEEP instruction is executed. To avoid the MCU entering the sleep mode unless it

is the programmers purpose, it is recommended to write the Sleep Enable (SE) bit to

one just before the execution of the SLEEP instruction and to clear it immediately after

waking up.

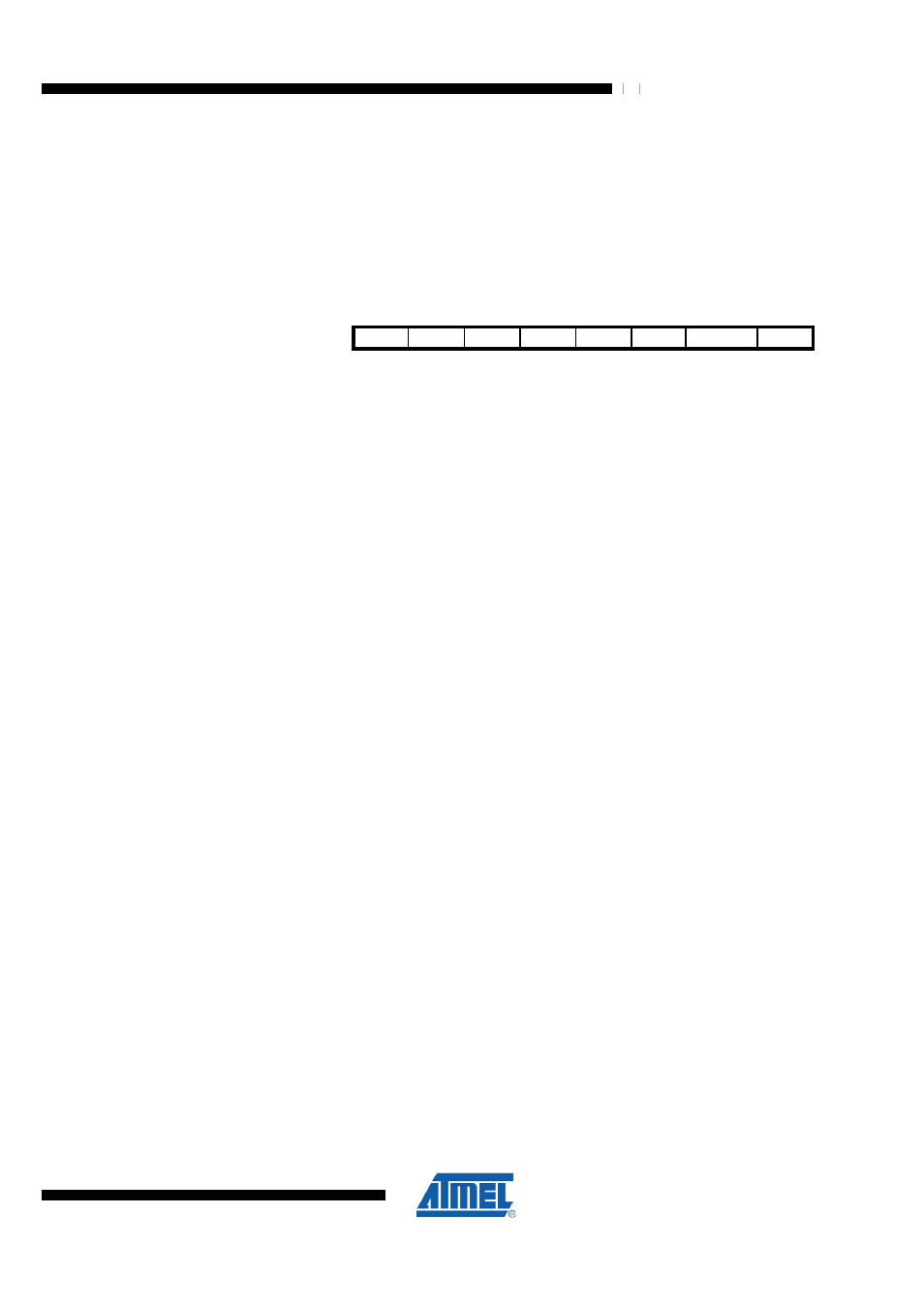

12.6.2 PRR0 – Power Reduction Register0

Bit

7

6

5

4

3

2

1

0

NA ($64)

PRTWI

PRTIM2 PRTIM0 PRPGA PRTIM1

PRSPI

PRUSART0 PRADC

PRR0

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

•

Bit 7 – PRTWI - Power Reduction TWI

Writing a logic one to this bit shuts down the TWI by stopping the clock to the module.

When waking up the TWI again, the TWI should be re initialized to ensure proper

operation.

•

Bit 6 – PRTIM2 - Power Reduction Timer/Counter2

Writing a logic one to this bit shuts down the Timer/Counter2 module. When the

Timer/Counter2 is enabled, operation will continue like before the shutdown.

•

Bit 5 – PRTIM0 - Power Reduction Timer/Counter0

Writing a logic one to this bit shuts down the Timer/Counter0 module. When the

Timer/Counter0 is enabled, operation will continue like before the shutdown.

•

Bit 4 – PRPGA - Power Reduction PGA

Writing a logic one to this bit reduced the power consumption of the programmable gain

amplifier. The block is not turned off. Only the current levels in the amplifiers are

reduced. Reducing the PGA current levels is only recommended for slow ADC clock

frequencies. A new ADC conversion using the PGA should be delayed by a default

start-up time after changing (setting or resetting) this bit.

•

Bit 3 – PRTIM1 - Power Reduction Timer/Counter1

Writing a logic one to this bit shuts down the Timer/Counter1 module. When the

Timer/Counter1 is enabled, operation will continue like before the shutdown.

•

Bit 2 – PRSPI - Power Reduction Serial Peripheral Interface

Writing a logic one to this bit shuts down the Serial Peripheral Interface by stopping the

clock to the module. When waking up the SPI again, the SPI should be re initialized to

ensure proper operation.

•

Bit 1 – PRUSART0 - Power Reduction USART

Writing a logic one to this bit shuts down the USART0 by stopping the clock to the

module. When waking up the USART0 again, the USART0 should be reinitialized to

ensure proper operation.

•

Bit 0 – PRADC - Power Reduction ADC

Writing a logic one to this bit shuts down the ADC. The ADC must be disabled (reset

ADEN bit in register ADCSRA) before shut down. The analog comparator cannot use

the ADC input MUX when the ADC is shut down.