29 scirqm - symbol counter interrupt mask register, Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 146

146

8266A-MCU Wireless-12/09

ATmega128RFA1

This interrupt indicates a compare match on compare unit 3.

•

Bit 1 – IRQSCP2 - Compare Unit 2 Compare Match IRQ

This interrupt indicates a compare match on compare unit 2.

•

Bit 0 – IRQSCP1 - Compare Unit 1 Compare Match IRQ

This interrupt indicates a compare match on compare unit 1.

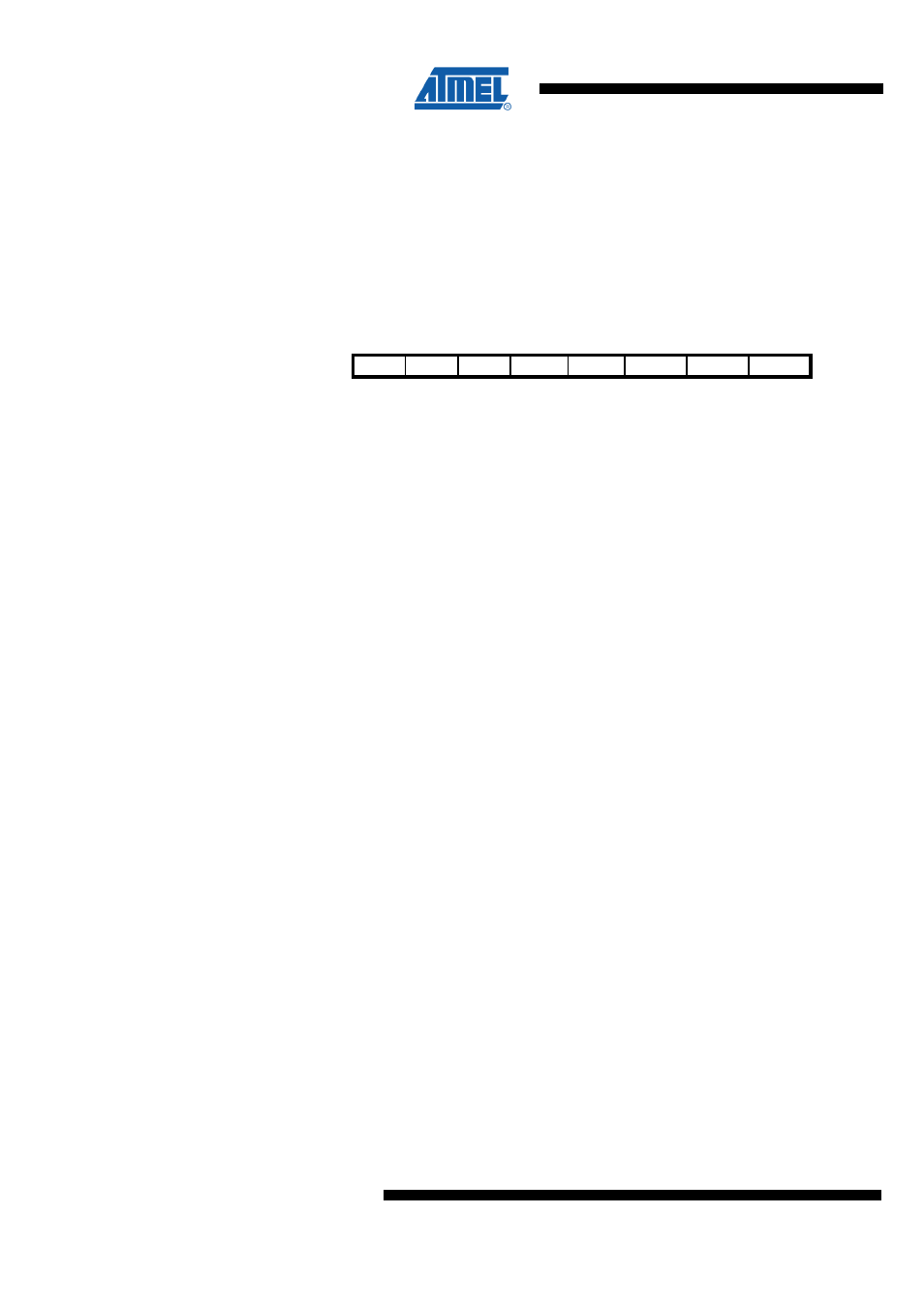

10.11.29 SCIRQM – Symbol Counter Interrupt Mask Register

Bit

7

6

5

4

3

2

1

0

NA ($DF)

Res2

Res1

Res0

IRQMBO IRQMOF IRQMCP3 IRQMCP2 IRQMCP1 SCIRQM

Read/Write

R

R

R

RW

RW

RW

RW

RW

Initial Value

0

0

0

0

0

0

0

0

The Interrupt Mask Register is used to enable corresponding interrupts. After reset all

interrupts are disabled. Disabled interrupts are still captured in the interrupt status

register SCIRQS, but no interrupt is requested. Before enabling an interrupt, the

corresponding interrupt status bit should be cleared by writing a 1. If the status bit is set

and the IRQ gets enabled, the IRQ handler is called immediatly.

•

Bit 7:5 – Res2:0 - Reserved Bit

This bit is reserved for future use. The result of a read access is undefined. The register

bit must always be written with the reset value.

•

Bit 4 – IRQMBO - Backoff Slot Counter IRQ enable

This bit enables the SCNT_BACKOFF interrupt.

•

Bit 3 – IRQMOF - Symbol Counter Overflow IRQ enable

This bit enables the SCNT_OVFL interrupt.

•

Bit 2 – IRQMCP3 - Symbol Counter Compare Match 3 IRQ enable

This bit enables the SCNT_CMP3 interrupt.

•

Bit 1 – IRQMCP2 - Symbol Counter Compare Match 2 IRQ enable

This bit enables the SCNT_CMP2 interrupt.

•

Bit 0 – IRQMCP1 - Symbol Counter Compare Match 1 IRQ enable

This bit enables the SCNT_CMP1 interrupt.