1 description of rx_aack configuration bits, Description of rx_aack configuration bits" on, Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 49

49

8266A-MCU Wireless-12/09

ATmega128RFA1

9.4.2.3.1 Description of RX_AACK Configuration Bits

Overview

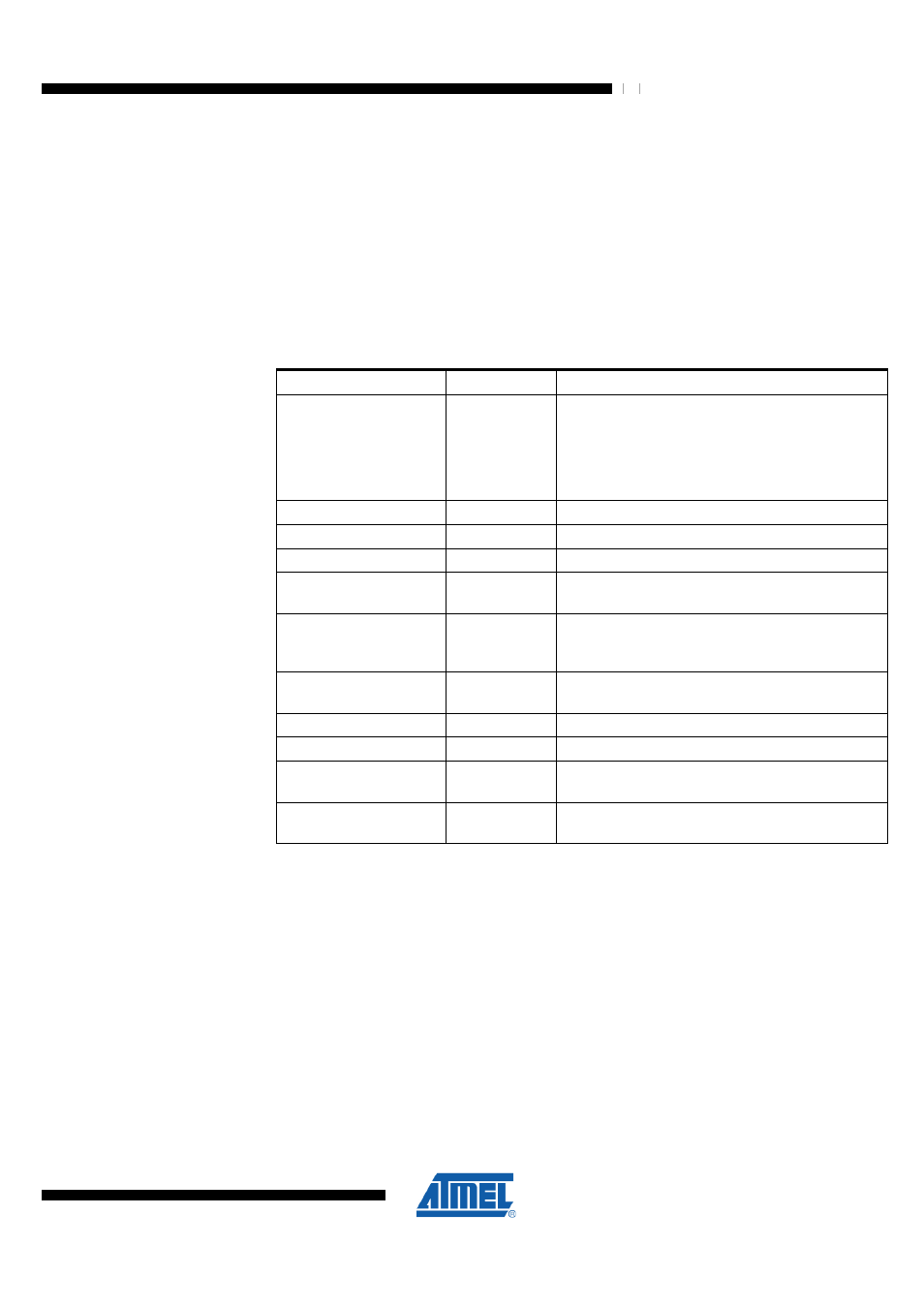

The following table summarizes all register bits which affect the behavior of a

RX_AACK transaction. For address filtering it is further required to setup address

registers to match to the expected address.

Configuration and address bits are to be set in TRX_OFF or PLL_ON state prior to

switching to RX_AACK mode.

A graphical representation of various operating modes is illustrated in

Table 9-5. Overview of RX_AACK Configuration Bits

Register Name

Register Bits

Description

SHORT_ADDR_0/1

PAN_ADDR_0/1

IEEE_ADDR_0

…

IEEE_ADDR_7

Set node addresses

RX_SAFE_MODE

7

Protect buffer after frame receive

AACK_PROM_MODE

1

Support promiscuous mode

AACK_ACK_TIME

2

Change auto acknowledge start time

AACK_UPLD_RES_FT

4

Enable reserved frame type reception, needed to

receive non-standard compliant frames

AACK_FLTR_RES_FT

5

Filter reserved frame types like data frame type,

needed for filtering of non-standard compliant

frames

SLOTTED_OPERATION

0

If set, acknowledgment transmission has to be

triggered by register bit SLPTR

AACK_I_AM_COORD

3

If set, the device is a PAN coordinator

AACK_DIS_ACK

4

Disable generation of acknowledgment

AACK_SET_PD

5

Set frame pending subfield in Frame Control Field

(FCF), refer to section

AACK_FVN_MODE

7:6

Controls the ACK behavior, depending on FCF

frame version number

The usage of the RX_AACK configuration bits for various operating modes of a node is

explained in the following sections. Configuration bits not mentioned in the following two

sections should be set to their reset values

.

Note, that the general behavior of the Extended Feature Set settings:

•

OQPSK_DATA_RATE

(PSDU data rate)

•

SFD_VALUE

(alternative SFD value)

•

ANT_DIV

(Antenna Diversity)

•

RX_PDT_LEVEL

(blocking frame reception of lower power signals)

are completely independent from RX_AACK mode (see

)

.

Each of these operating modes can be combined with the

RX_AACK mode.