19 timer/counter 0, 1, 3, 4, and 5 prescaler, 1 internal clock source, 2 prescaler reset – Rainbow Electronics ATmega128RFA1 User Manual

Page 304: 3 external clock source, Atmega128rfa1

304

8266A-MCU Wireless-12/09

ATmega128RFA1

19 Timer/Counter 0, 1, 3, 4, and 5 Prescaler

Timer/Counter 0, 1, 3, 4, and 5 share the same prescaler module, but the

Timer/Counters can have different prescaler settings. The description below applies to

all Timer/Counters. Tn is used as a general name, n = 0, 1, 3, 4, or 5.

19.1 Internal Clock Source

The Timer/Counter can be clocked directly by the system clock (by setting the CSn2:0 =

1). This provides the fastest operation with a maximum Timer/Counter clock frequency

equal to system clock frequency (f

CLK_I/O

). Alternatively one of four taps from the

prescaler can be used as a clock source. The prescaled clock has a frequency of either

f

CLK_I/O

/8, f

CLK_I/O

/64, f

CLK_I/O

/256 or f

CLK_I/O

/1024.

19.2 Prescaler Reset

The prescaler is free running, i.e., operates independently of the Clock Select logic of

the Timer/Counter, and it is shared by the Timer/Counter Tn. Since the prescaler is not

affected by the Timer/Counter’s clock select, the state of the prescaler will have

implications for situations where a prescaled clock is used. One example of prescaling

artifacts occurs when the timer is enabled and clocked by the prescaler (6 > CSn2:0 >

1). The number of system clock cycles from the moment the timer is enabled until the

first count occurs can be from 1 to N+1 system clock cycles, where N equals the

prescaler divisor (8, 64, 256, or 1024).

It is possible to use the prescaler reset for synchronizing the Timer/Counter to program

execution. However care must be taken if the other Timer/Counter that shares the same

prescaler also uses prescaling. A prescaler reset will affect the prescaler period for all

connected Timer/Counters.

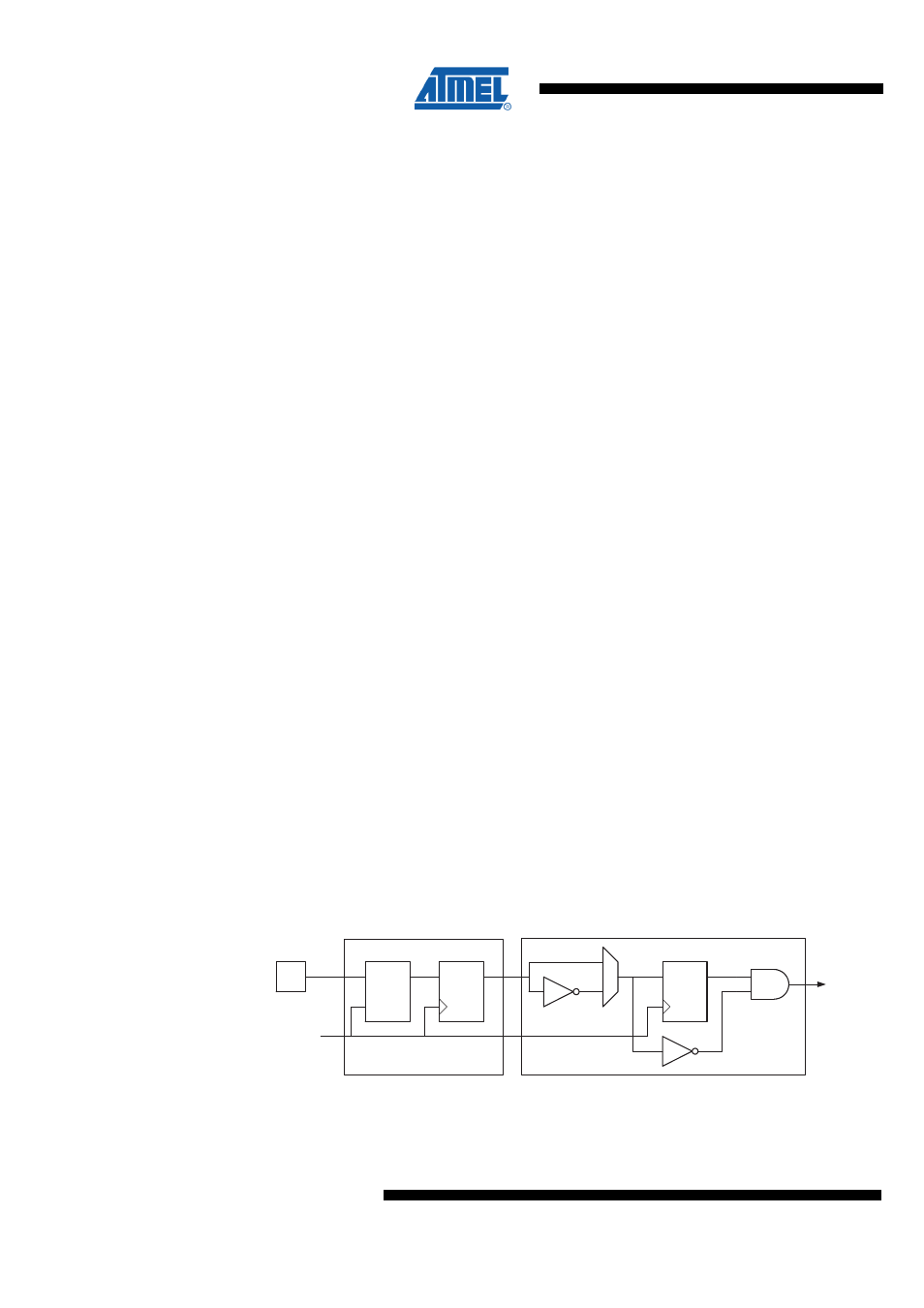

19.3 External Clock Source

An external clock source applied to the Tn pin can be used as Timer/Counter clock

(clk

Tn

). The Tn pin is sampled once every system clock cycle by the pin synchronization

logic. The synchronized (sampled) signal is then passed through the edge detector.

Figure 19-1 shows a functional equivalent block diagram of the Tn synchronization and

edge detector logic. The registers are clocked at the positive edge of the internal

system clock (clk

I/O

). The latch is transparent in the high period of the internal system

clock.

The edge detector generates one clk

Tn

pulse for each positive (CSn2:0 = 7) or negative

(CSn2:0 = 6) edge it detects.

Figure 19-1. Tn/T0 Pin Sampling

Tn_sync

(To Clock

Select Logic)

Edge Detector

Synchronization

D

Q

D

Q

LE

D

Q

Tn

clk

I/O

The synchronization and edge detector logic introduces a delay of 2.5 to 3.5 system

clock cycles from an edge applied to the Tn pin to the counter being updated.