4 tap controller, Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 437

437

8266A-MCU Wireless-12/09

ATmega128RFA1

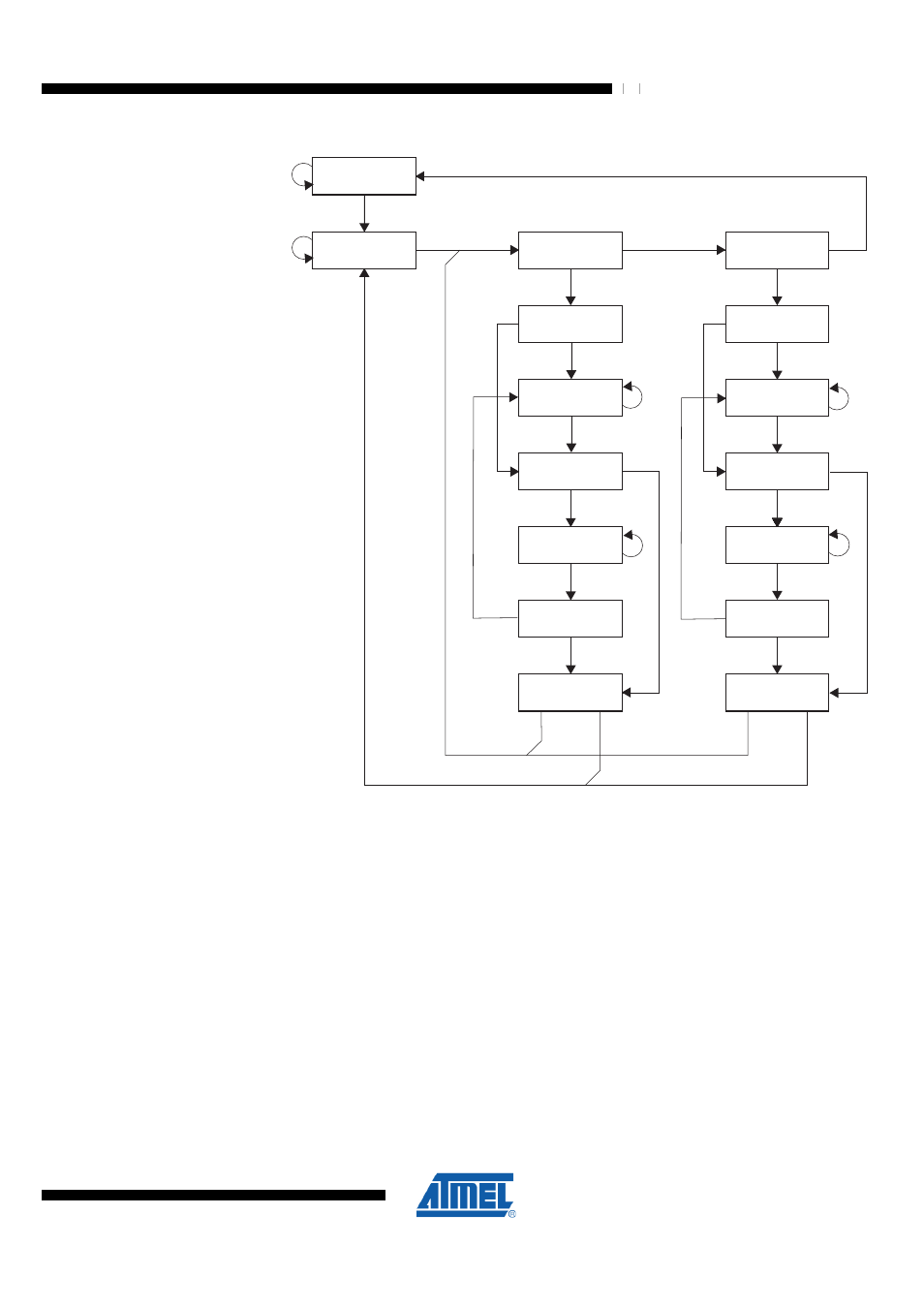

Figure 28-2. TAP Controller State Diagram

Test-Logic-Reset

Run-Test/Idle

Shift-DR

Exit1-DR

Pause-DR

Exit2-DR

Update-DR

Select-IR Scan

Capture-IR

Shift-IR

Exit1-IR

Pause-IR

Exit2-IR

Update-IR

Select-DR Scan

Capture-DR

0

1

0

1

1

1

0

0

0

0

1

1

1

0

1

1

0

1

0

0

1

0

1

1

0

1

0

0

0

0

1

1

28.4 TAP Controller

The TAP controller is a 16-state finite state machine that controls the operation of the

Boundary-scan circuitry, JTAG programming circuitry, or on-chip debug system. The

state transitions depicted in

depend on the signal present on TMS

(shown adjacent to each state transition) at the time of the rising edge at TCK. The

initial state after a Power-on Reset is Test-Logic-Reset.

As a definition in this document, the LSB is shifted in and out first for all Shift Registers.

Assuming Run-Test/Idle is the present state, a typical scenario for using the JTAG

interface is:

•

At the TMS input, apply the sequence 1, 1, 0, 0 at the rising edges of TCK to enter

the Shift Instruction Register – Shift-IR state. While in this state, shift the four bits of

the JTAG instructions into the JTAG Instruction Register from the TDI input at the

rising edge of TCK. The TMS input must be held low during input of the 3 LSBs in

order to remain in the Shift-IR state. The MSB of the instruction is shifted in when

this state is left by setting TMS high. While the instruction is shifted in from the TDI

pin, the captured IR-state 0x01 is shifted out on the TDO pin. The JTAG Instruction