2 nemcr - flash extended-mode control-register, Atmega128rfa1 – Rainbow Electronics ATmega128RFA1 User Manual

Page 463

463

8266A-MCU Wireless-12/09

ATmega128RFA1

instruction is executed within four clock cycles. The CPU is halted during the entire

page write operation if the NRWW section is addressed.

•

Bit 1 – PGERS - Page Erase

If this bit is written to one at the same time as SPMEN, the next SPM instruction within

four clock cycles executes page erase. The page address is taken from the high part of

the Z pointer. The data in R1 and R0 are ignored. The PGERS bit will auto-clear upon

completion of a page erase, or if no SPM instruction is executed within four clock

cycles. The CPU is halted during the entire page write operation if the NRWW section is

addressed.

•

Bit 0 – SPMEN - Store Program Memory Enable

This bit enables the SPM instruction for the next four clock cycles. If written to one

together with either RWWSRE, BLB-SET, PGWRT or PGERS, the following SPM

instruction will have a special meaning, see description above. If only SPMEN is written,

the following SPM instruction will store the value in R1:R0 in the temporary page buffer

addressed by the Z pointer. The LSB of the Z pointer is ignored. The SPMEN bit will

auto-clear upon completion of an SPM instruction, or if no SPM instruction is executed

within four clock cycles. During page erase and page write, the SPMEN bit remain high

until the operation is completed. Writing any other combination than "10001", "01001",

"00101", "00011" or "00001" in the lower five bits will have no effect.

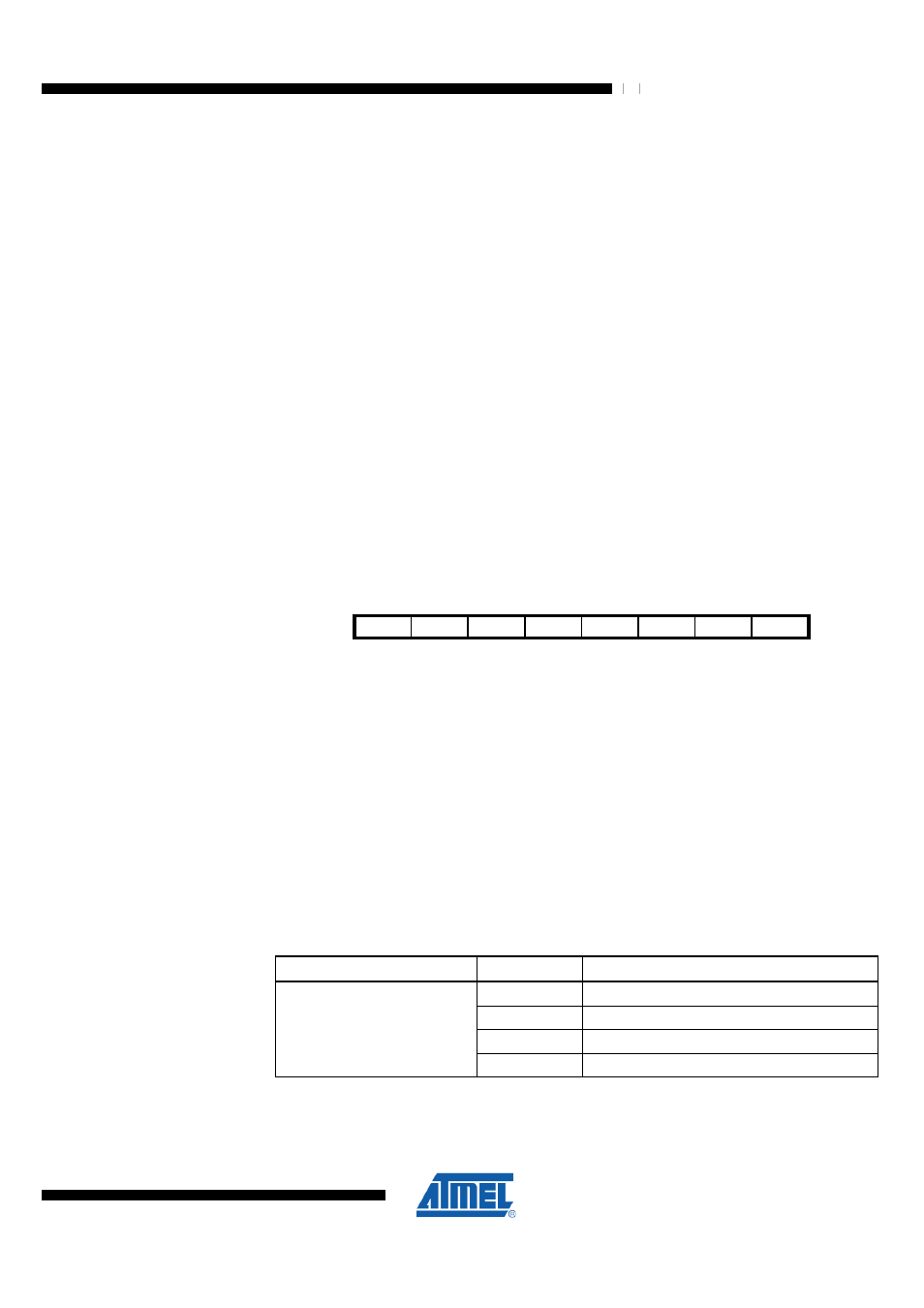

30.7.2 NEMCR – Flash Extended-Mode Control-Register

Bit

7

6

5

4

3

2

1

0

NA ($75)

Resx7

ENEAM

AEAM1

AEAM0

Resx3

Resx2

Resx1

Resx0

NEMCR

Read/Write

RW

RW

RW

RW

RW

RW

RW

RW

Initial Value

0

0

0

0

1

0

1

0

The Flash Extended-Mode Control-Register handles the extended address-mode of the

extra rows.

•

Bit 7 – Resx7 - Reserved

•

Bit 6 – ENEAM - Enable Extended Address Mode for Extra Rows

When active high, the extended address mode of the extra rows is enabled. The

address is decoded from bits AEAM1:0 of this register.

•

Bit 5:4 – AEAM1:0 - Address for Extended Address Mode of Extra Rows

These bits are only used when bit ENEAM of this register is set high. Then AEAM1:0

are used to decode the addresses of the extra rows. A value of 0 decodes the default

factory row that is also accessible when the extended address mode is deactivated.

Table 30-8 AEAM Register Bits

Register Bits

Value

Description

0

Factory Row

1

User Row 1

2

User Row 2

AEAM1:0

3

User Row 3

•

Bit 3:0 – Resx3:0 - Reserved