1 transmitter and receiver flags and interrupts, 2 disabling the transmitter or receiver, 6 usart mspim register description – Rainbow Electronics ATmega128RFA1 User Manual

Page 373: 1 udrn - usart mspim i/o data register, Atmega128rfa1

373

8266A-MCU Wireless-12/09

ATmega128RFA1

24.5.1 Transmitter and Receiver Flags and Interrupts

The RXCn, TXCn, and UDREn flags and corresponding interrupts in USART in MSPIM

mode are identical in function to the normal USART operation. However, the receiver

error status flags (FE, DOR, and PE) are not in use and are always read as zero.

24.5.2 Disabling the Transmitter or Receiver

The disabling of the transmitter or receiver in USART in MSPIM mode is identical in

function to the normal USART operation.

24.6 USART MSPIM Register Description

The following section describes the registers used for SPI operation using the USART.

24.6.1 UDRn – USART MSPIM I/O Data Register

The function and bit description of the USART data register (UDRn) in MSPI mode is

identical to normal USART operation. See

"UDR0 – USART0 I/O Data Register" on

.

24.6.2 UBRRnL and UBRRnH – USART MSPIM Baud Rate Registers

The function and bit description of the baud rate registers in MSPI mode is identical to

normal USART operation. See

"UBRR0L – USART0 Baud Rate Register Low Byte" on

and

"UBRR0H – USART0 Baud Rate Register High Byte" on page 360

.

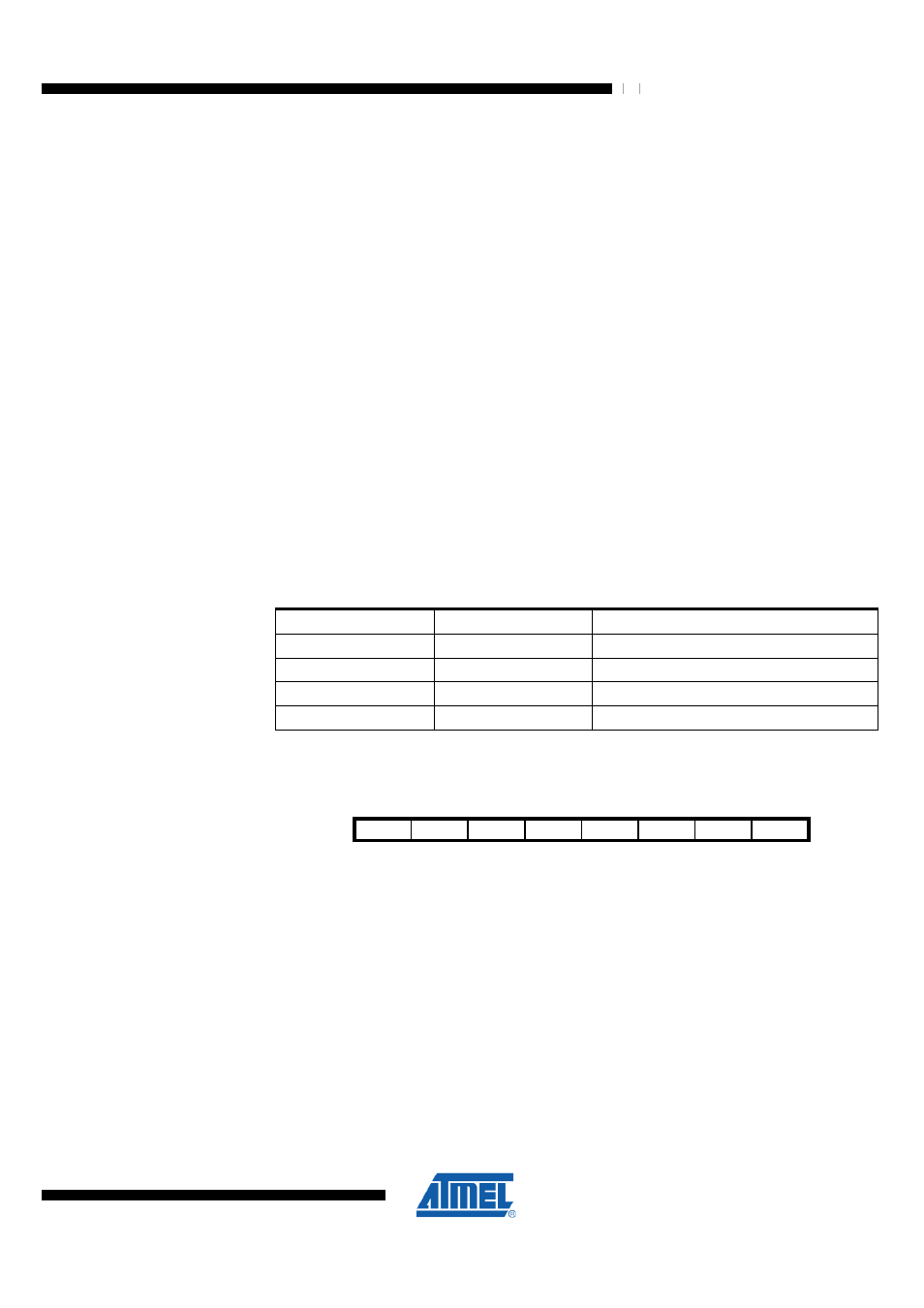

Table 24–3. Comparison of USART in MSPIM mode and SPI pins

USART_MSPIM

SPI

Comment

TxDn

MOSI

Master Out only

RxDn

MISO

Master In only

XCKn

SCK

(Functional identical)

(N/A)

SS

¯ ¯

Not supported by USART in MSPIM

24.6.3 UCSR0A – USART0 MSPIM Control and Status Register A

Bit

7

6

5

4

3

2

1

0

NA ($C0)

RXC0

TXC0

UDRE0

UCSR0A

Read/Write

R

RW

R

Initial Value

0

0

0

•

Bit 7 – RXC0 - USART Receive Complete

This flag bit is set when there are unread data in the receive buffer and cleared when

the receive buffer is empty (i.e., does not contain any unread data). If the Receiver is

disabled, the receive buffer will be flushed and consequently the RXC0 bit will become

zero. The RXC0 Flag can be used to generate a Receive Complete interrupt (see

description of the RXCIE0 bit).

•

Bit 6 – TXC0 - USART Transmit Complete

This flag bit is set when the entire frame in the Transmit Shift Register has been shifted

out and there are no new data currently present in the transmit buffer (UDR0). The

TXC0 Flag bit is automatically cleared when a transmit complete interrupt is executed,

or it can be cleared by writing a one to its bit location. The TXC0 Flag can generate a

Transmit Complete interrupt (see description of the TXCIE0 bit).