3 prr1 - power reduction register 1, 4 prr2 - power reduction register 2, Prr2 – power – Rainbow Electronics ATmega128RFA1 User Manual

Page 168: Atmega128rfa1

168

8266A-MCU Wireless-12/09

ATmega128RFA1

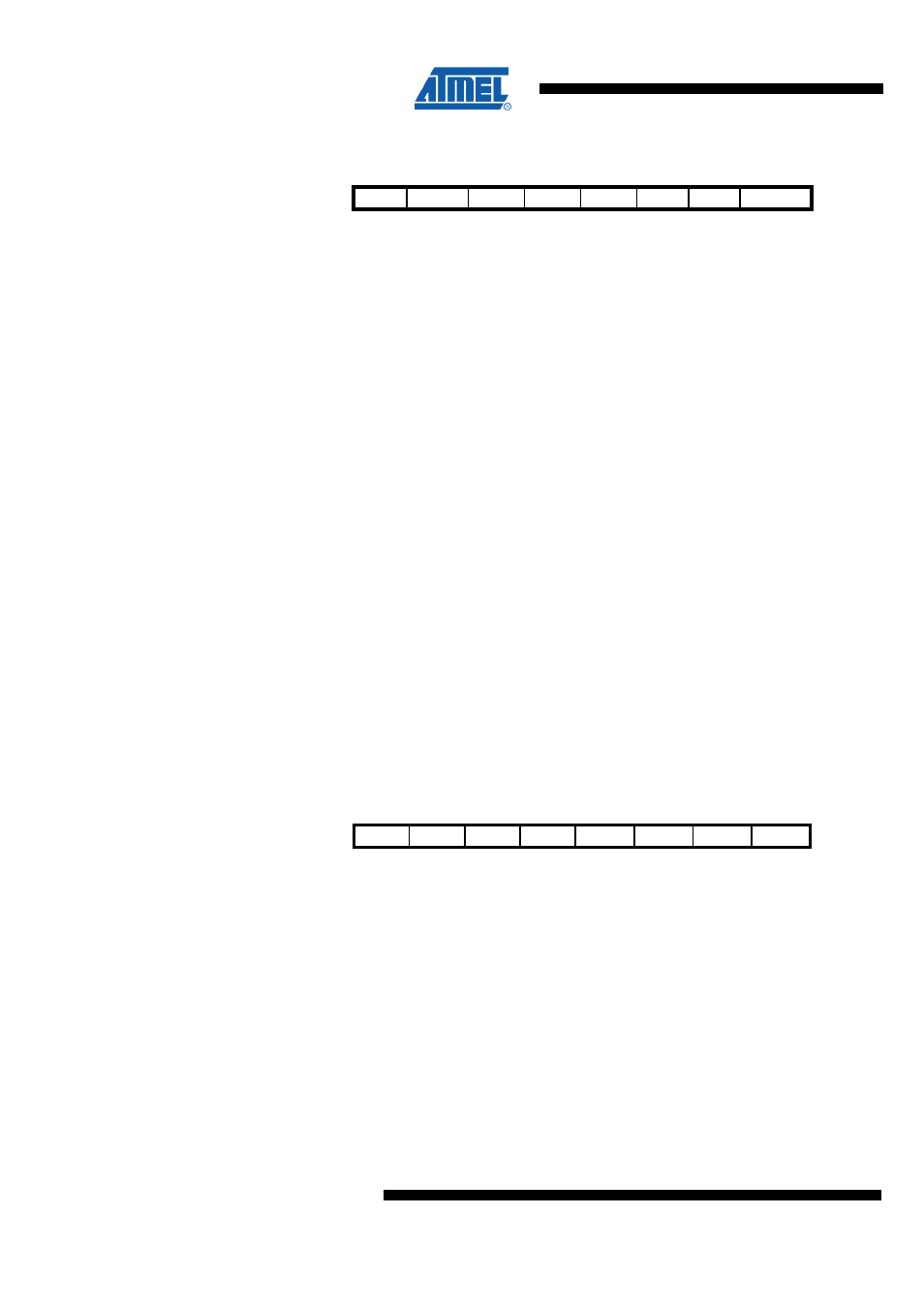

12.6.3 PRR1 – Power Reduction Register 1

Bit

7

6

5

4

3

2

1

0

NA ($65)

Res

PRTRX24 PRTIM5 PRTIM4 PRTIM3

PRUSART1

PRR1

Read/Write

R

RW

RW

RW

RW

RW

Initial Value

0

0

0

0

0

0

•

Bit 7 – Res - Reserved Bit

This bit is reserved for future use. A read access always will return zero. A write access

does not modify the content.

•

Bit 6 – PRTRX24 - Power Reduction Transceiver

Writing a logic one to this bit shuts down the transceiver (disconnect from the power

supply). In power-down and power-save modes the power-chain will be disabled when

this bit is one. Writing a logic zero to this bit will re-enable the transceiver.

•

Bit 5 – PRTIM5 - Power Reduction Timer/Counter5

Writing a logic one to this bit shuts down the Timer/Counter5 module. When the

Timer/Counter5 is enabled, operation will continue like before the shutdown.

•

Bit 4 – PRTIM4 - Power Reduction Timer/Counter4

Writing a logic one to this bit shuts down the Timer/Counter4 module. When the

Timer/Counter4 is enabled, operation will continue like before the shutdown.

•

Bit 3 – PRTIM3 - Power Reduction Timer/Counter3

Writing a logic one to this bit shuts down the Timer/Counter3 module. When the

Timer/Counter3 is enabled, operation will continue like before the shutdown.

•

Bit 0 – PRUSART1 - Power Reduction USART1

Writing a logic one to this bit shuts down the USART1 by stopping the clock to the

module. When waking up the USART1 again, the USART1 should be reinitialized to

ensure proper operation.

12.6.4 PRR2 – Power Reduction Register 2

Bit

7

6

5

4

3

2

1

0

NA ($63)

Res3

Res2

Res1

Res0

PRRAM3 PRRAM2 PRRAM1 PRRAM0

PRR2

Read/Write

R

R

R

R

RW

RW

RW

RW

Initial Value

0

0

0

0

0

0

0

0

The Power Reduction Register PRR2 allows to individually disable all four SRAM

blocks. Setting any PRRAM3:0 bit to one will completely switch off (disconnect from the

power supply) the corresponding SRAM block. This enables the application to disable

unused SRAM memory to save power. Every SRAM block can be re-enabled by

reseting the appropriate PRRAM3:0 bit.

•

Bit 7:4 – Res3:0 - Reserved Bit

This bit is reserved for future use. A read access always will return zero. A write access

does not modify the content.

•

Bit 3 – PRRAM3 - Power Reduction SRAM 3

Setting this bit to one will disable the SRAM block 3. Setting this bit to zero will enable

the SRAM block 3.