5 categories & use of application instructions – Delta Electronics Programmable Logic Controller DVP-PLC User Manual

Page 196

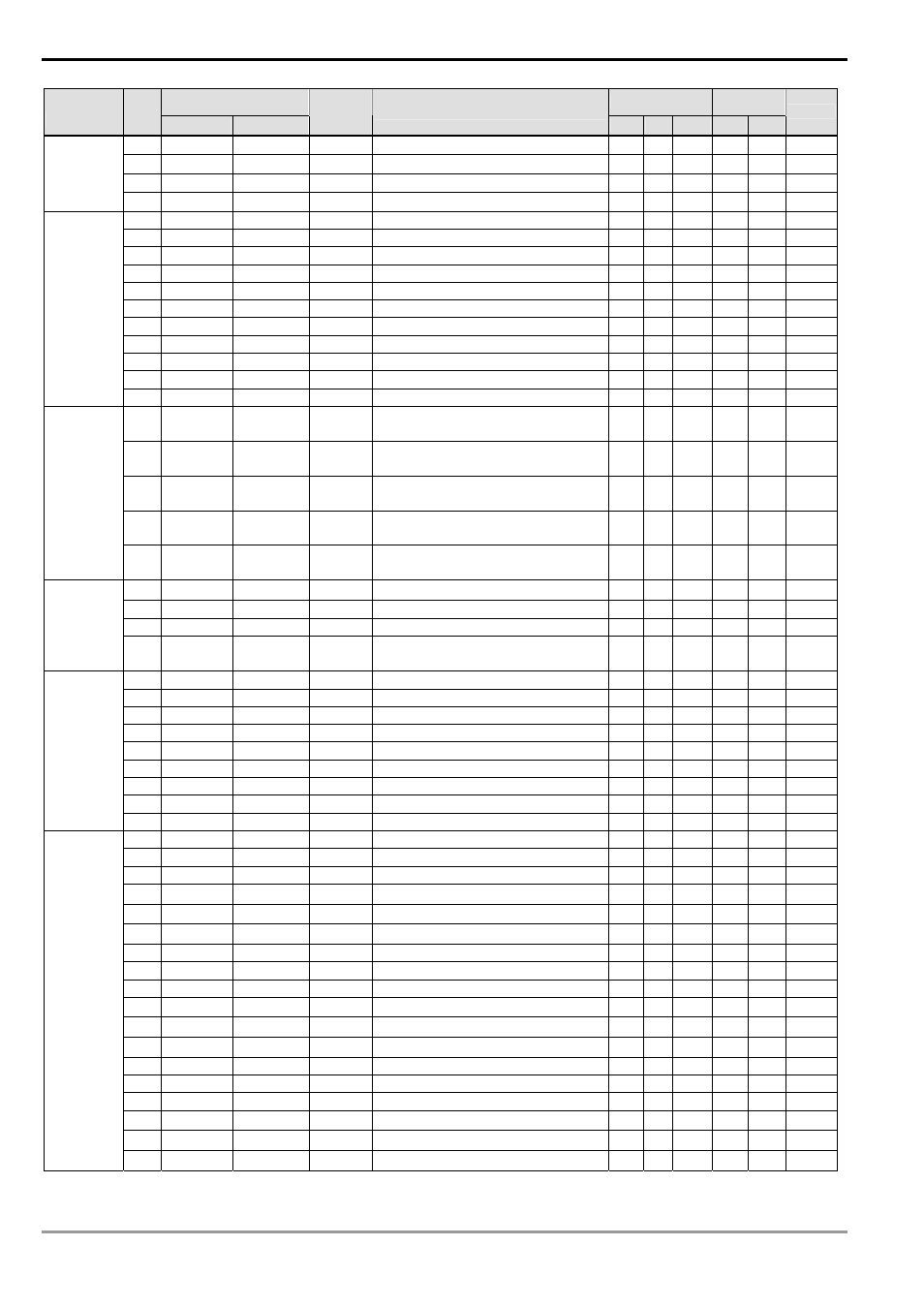

5 Categories & Use of Application Instructions

DVP-PLC Application Manual

5-4

172

- DADDR

3

Floating Point Addition

3

3

3

- 13

9-51

173

- DSUBR

3

Floating Point Subtraction

3

3

3

- 13

9-53

174

- DMULR

3

Floating Point Multiplication

3

3

3

- 13

9-55

Floating

Point

Oper

ation

175

- DDIVR

3

Floating Point Division

3

3

3

- 13

9-57

180

MAND -

3

Matrix ‘AND’ Operation

-

3

3

9 -

9-59

181

MOR -

3

Matrix ‘OR’ Operation

-

3

3

9 -

9-61

182

MXOR -

3

Matrix ‘XOR’ Operation

-

3

3

9 -

9-62

183

MXNR -

3

Matrix ‘XNR’ Operation

-

3

3

9 -

9-63

184

MINV -

3

Matrix Inverse Operation

-

3

3

7 -

9-64

185

MCMP -

3

Matrix Compare

-

3

3

9 -

9-65

186

MBRD -

3

Read Matrix Bit

-

3

3

7 -

9-67

187

MBWR -

3

Write Matrix Bit

-

3

3

7 -

9-69

188

MBS -

3

Matrix Bit Displacement

-

3

3

7 -

9-71

189

MBR -

3

Matrix Bit Rotation

-

3

3

7 -

9-73

Matrix

190

MBC -

3

Matrix Bit Status Counting

-

3

3

7 -

9-75

191

- DPPMR

-

2-Axis Relative Point to Point

Motion (*)

-

-

3

- 17

9-76

192

- DPPMA

-

2-Axis Absolute Point to Point

Motion (*)

-

-

3

- 17

9-79

193

- DCIMR

-

2-Axis Relative Position Arc

Interpolation (*)

-

-

3

- 17

9-81

194

- DCIMA

-

2-Axis Absolute Position Arc

Interpolation (*)

-

-

–

- 17

9-86

Positioning Instruction

195

- DPTPO

-

Single-Axis Pulse Output by Table

(*)

-

-

–

- 13

9-91

196

HST -

3

High Speed Timer

-

-

3

3

–

9-93

197

- DCLLM

-

Close Loop Position Control (*)

-

-

3

- 17

9-95

202

SCAL -

3

Proportional Value Calculation

3

3

3

9 - 10-1

203

SCLP -

3

Parameter Proportional Value

Calculation

3

3

3

9 - 10-3

215

LD& DLD&

-

S

1

& S

2

-

3

3

5 9 10-7

216

LD| DLD|

-

S

1

| S

2

-

3

3

5 9 10-7

217

LD^ DLD^

-

S

1

^ S

2

-

3

3

5 9 10-7

218

AND& DAND&

- S

1

& S

2

-

3

3

5 9 10-8

219

AND| DAND|

- S

1

| S

2

-

3

3

5 9 10-8

220

AND^ DAND^

- S

1

^ S

2

-

3

3

5 9 10-8

221

OR& DOR&

- S

1

& S

2

-

3

3

5 9 10-9

222

OR| DOR|

-

S

1

| S

2

-

3

3

5 9 10-9

Cont

act T

ype

Logi

c

Operation

223

OR^ DOR^

-

S

1

^ S

2

-

3

3

5 9 10-9

224

LD= DLD=

-

S

1

= S

2

3

3

3

5 9 10-10

225

LD> DLD>

-

S

1

> S

2

3

3

3

5 9 10-10

226

LD< DLD<

-

S

1

< S

2

3

3

3

5 9 10-10

228

LD<> DLD<>

- S

1

≠ S

2

3

3

3

5 9 10-10

229

LD<= DLD<=

- S

1

≦ S

2

3

3

3

5 9 10-10

230

LD>= DLD>=

- S

1

≧ S

2

3

3

3

5 9 10-10

232

AND= DAND=

- S

1

= S

2

3

3

3

5 9 10-11

233

AND> DAND>

- S

1

> S

2

3

3

3

5 9 10-11

234

AND< DAND<

- S

1

< S

2

3

3

3

5 9 10-11

236

AND<> DAND<>

- S

1

≠ S

2

3

3

3

5 9 10-11

237

AND<= DAND<=

- S

1

≦ S

2

3

3

3

5 9 10-11

238

AND>= DAND>=

- S

1

≧ S

2

3

3

3

5 9 10-11

240

OR= DOR=

- S

1

= S

2

3

3

3

5 9 10-12

241

OR> DOR>

- S

1

> S

2

3

3

3

5 9 10-12

242

OR< DOR<

- S

1

< S

2

3

3

3

5 9 10-12

244

OR<> DOR<>

- S

1

≠ S

2

3

3

3

5 9 10-12

245

OR<= DOR<=

- S

1

≦ S

2

3

3

3

5 9 10-12

Cont

act T

ype

Com

pa

rison

Instru

ction

246

OR>= DOR>=

- S

1

≧ S

2

3

3

3

5 9 10-12

Instructions marked with * are available in EH2/SV series MPU.

Mnemonic

Applicable to

STEPS

Category

A PI

16-bit

32-bit

P

instruction

Function

ES

SA

EH 16-bit 32-bit

Page