2 functions of devices in dvp-plc – Delta Electronics Programmable Logic Controller DVP-PLC User Manual

Page 124

2 Functions of Devices in DVP-PLC

DVP-PLC Application Manual

2-96

4. D1145: Number of special left-side extension modules (AD, DA, XA, PT, TC…); Max. 8 (available in SV only)

Function Group

Adjustable Pulse Speed Acceleration/Deceleration

Number

M1144 ~ M1149, M1154, D1030, D1031, D1144, D1154, D1155

Contents:

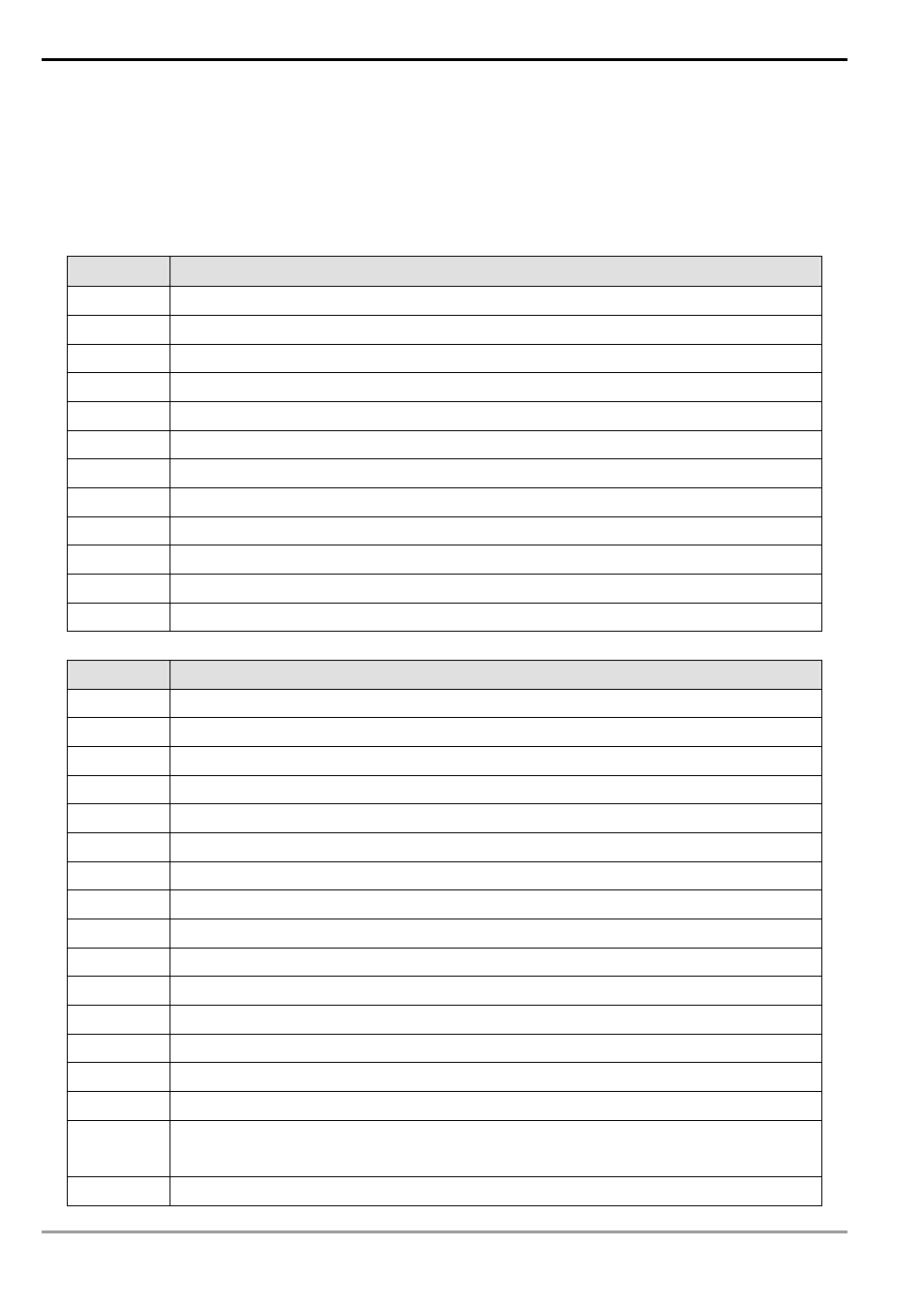

1. Special D and special M of Y0 adjustable pulse speed acceleration/deceleration for SA/SX/SC:

Device No.

Function

M1144

Activation switch for Y0 adjustable pulse speed acceleration/deceleration

M1145

Accerlerating flag for Y0 adjustable pulse speed acceleration/deceleration

M1146

“Target frequency reached” flag for Y0 adjustable pulse speed acceleration/deceleration

M1147

“Decerlerating” flag for Y0 adjustable pulse speed acceleration/deceleration

M1148

“Function completed” flag for Y0 adjustable pulse speed acceleration/deceleration

M1149

“Counting temporarily stops” flag for Y0 adjustable pulse speed acceleration/deceleration

M1154

“Enabling deceleration” flag for Y0 adjustable pulse speed acceleration/deceleration

D1030

The lower 16 bits in the 32-bit data register for accumulative Y0 output pulses

D1031

The higher 16 bits in the 32-bit data register for accumulative Y0 output pulses

D1144

Starting No. of the register (D) for Y0 adjustable pulse speed acceleration/deceleration

D1154

Recommended value for indicated gap time of deceleration(10 ~ 32,767 ms)

D1155

Recommended value for indicated gap frequency of deceleration (-1 ~ -32,700 Hz)

2. Parameters for D1144:

Index

Function

+ 0

Total number of sections (n) (max. 10)

+ 1

Currently executed section (read only)

+ 2

Start frequency of the 1

st

section (SF1)

+ 3

Gap time of the 1

st

section (GT1)

+ 4

Gap frequency of the 1

st

section (GF1)

+ 5

Target frequency of the 1

st

section (TF1)

+ 6

The lower 16 bits of the 32 bits for the target number of output pulses in the 1

st

section (SE1)

+ 7

The higher 16 bits of the 32 bits for the target number of output pulses in the 1

st

section (SE1)

+ 8

Start frequency of the 2

nd

section (SF2); Cannot be the same as TF1

+ 9

Gap time of the 2

nd

section (GT2)

+ 10

Gap frequency of the 2

nd

section (GF2)

+ 11

Target frequency of the 2

nd

section (TF2)

+ 12

The lower 16 bits of the 32 bits for the target number of output pulses in the 2

nd

section (SE2)

+ 13

The higher 16 bits of the 32 bits for the target number of output pulses in the 2

nd

section (SE2)

: :

+ n*6 + 2

Start frequency of the n

th

section (SFn); Cannot be the same as the start frequency of the n-1

th

section (TFn-1)

+ n*6 + 3

Gap time of the n

th

section (GTn)