2 address allocation, 1 operand directory, 2 addressing the memory – HEIDENHAIN TNC 407 (243 020) Technical Manual User Manual

Page 479: 2 address allocation 2.2.1 operand directory

2.2 Address allocation

2.2.1 Operand directory

Operand

Abbreviation

Address range

Marker

M (Marker)

0 to 3023

Input

I (Input)

I0 to I31; I128 to I152;

I64 to I126 (first extension board);

I192 to I254 (second extension board)

Output

O (Output)

O0 to O30;

O32 to O62(first extension board);

O64 to O94 (second extension board);

Counter

C (Counter)

Set counter : C0 to C31

Counter contents: C48 to C79

Release count pulse: C96 to C127

Timer

T (Timer)

Timer start: T0 to T47

Timer running: T48 to T95

Byte

B (Byte)

0 to 1023 (8 Bit)

Word

W (Word)

0 to 1022 (16 Bit)

Doubleword

D (Doubleword)

0 to 1020 (32 Bit)

Constant

K

- 2 147 483 647 to + 2 147 483 647

2.2.2 Addressing the memory

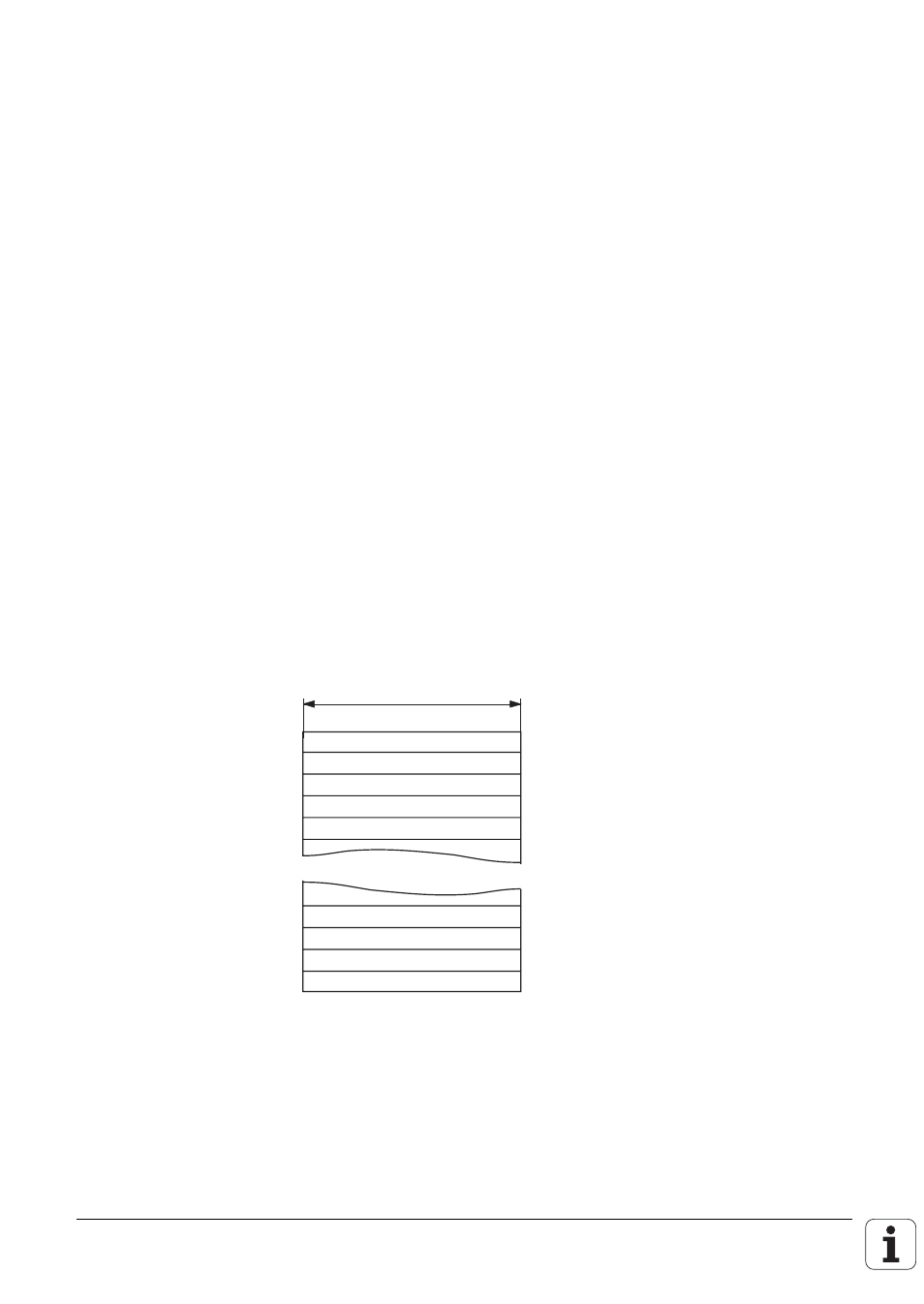

The memory for the Operands B (8 Bit), W (16 Bit), D (32 Bit) is only 8 Bit wide. Since the Operands

can be 8,16 or 32 Bit wide, an overlap of the memory areas will occur, which must be taken into

account in addressing the memory.

8 bit

0

7

B0

B1023

B1022

B1021

B1020

D1020 W1020

B1

B2

B3

B4

B5

W0

D0

W2

W4

D4

W1022

..

.

..

.

..

.

..

.

➞ High-Byte for W; Highest-Byte for D

➞ Lowest-Byte for D

➞ Low-Byte for W

In Byte addressing every address from 0 to 1023 is accessible. In Word addressing, every second

address from 0 to 1022 is accessible and in Doubleword addressing every fourth from 0 to 1020.

The address parameter gives the High Byte for a Word Address (W) , or the Highest Byte for a

Doubleword address (D).