Renesas SH7641 User Manual

Page 99

Section 2 CPU

Rev. 4.00 Sep. 14, 2005 Page 49 of 982

REJ09B0023-0400

Addressing

Mode

Instruction

Format

Effective Address Calculation Method

Calculation Formula

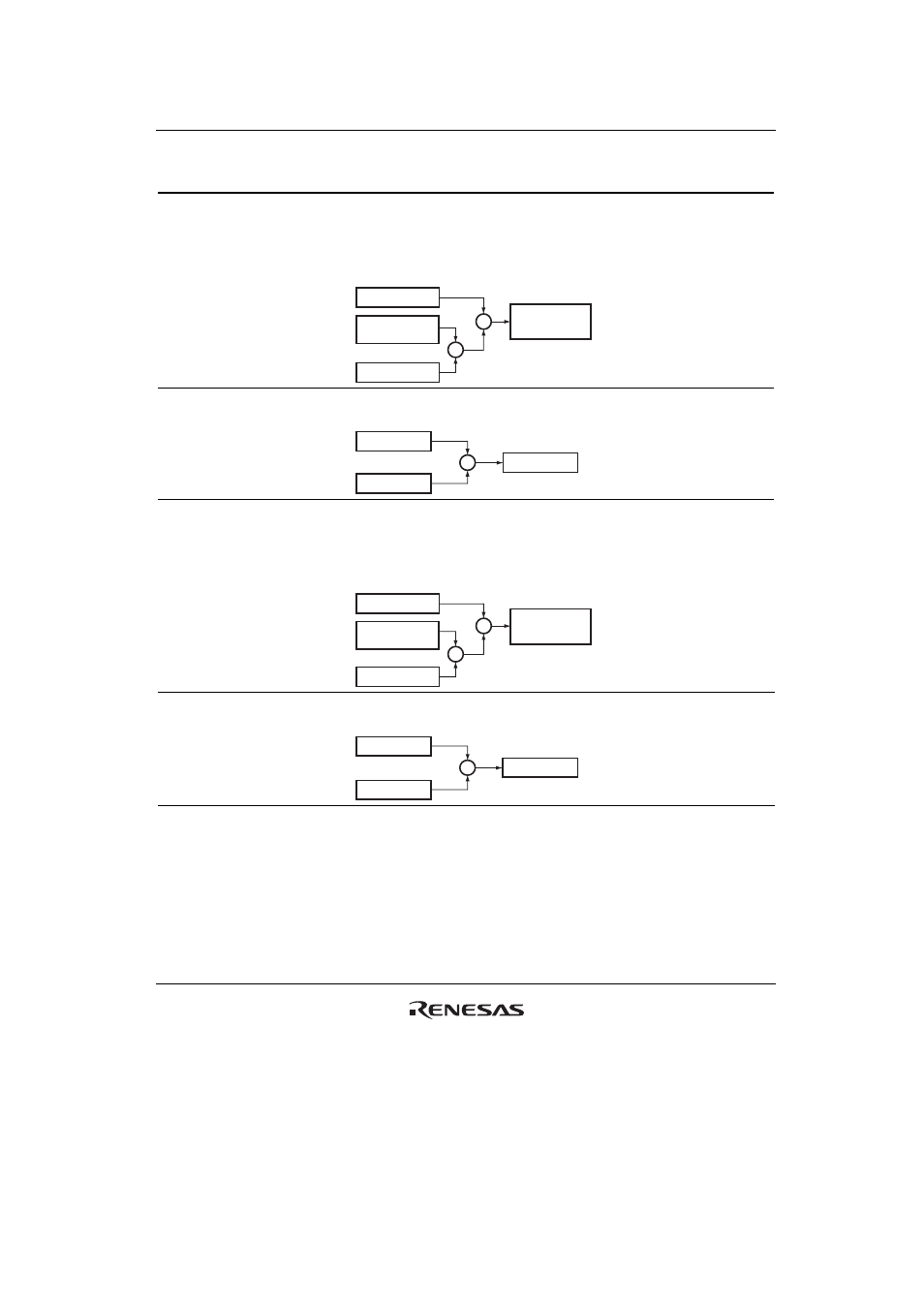

Register

indirect with

displacement

@(disp:4, Rn)

Effective address is register Rn contents with

4-bit displacement disp added. After disp is

zero-extended, it is multiplied by 1 (byte),

2 (word), or 4 (longword), according to the

operand size.

Rn

1/2/4

+

×

disp

(zero-extended)

Rn

+ disp

× 1/2/4

Byte: Rn + disp

Word: Rn + disp

× 2

Longword: Rn + disp

× 4

Indexed

register indirect

@(R0, Rn)

Effective address is sum of register Rn and

R0 contents.

Rn

R0

Rn + R0

+

Rn + R0

GBR

indirect with

displacement

@(disp:8, GBR)

Effective address is register GBR contents

with 8-bit displacement disp added.

After disp is zero-extended, it is multiplied by

1 (byte), 2 (word), or 4 (longword), according

to the operand size.

GBR

1/2/4

+

×

disp

(zero-extended)

GBR

+ disp

× 1/2/4

Byte: GBR + disp

Word: GBR + disp

× 2

Longword: GBR + disp

× 4

Indexed GBR

indirect

@(R0, GBR)

Effective address is sum of register GBR and

R0 contents.

GBR

R0

GBR + R0

+

GBR + R0