2 register descriptions, 1 watchdog timer counter (wtcnt) – Renesas SH7641 User Manual

Page 206

Section 5 Watchdog Timer (WDT)

Rev. 4.00 Sep. 14, 2005 Page 156 of 982

REJ09B0023-0400

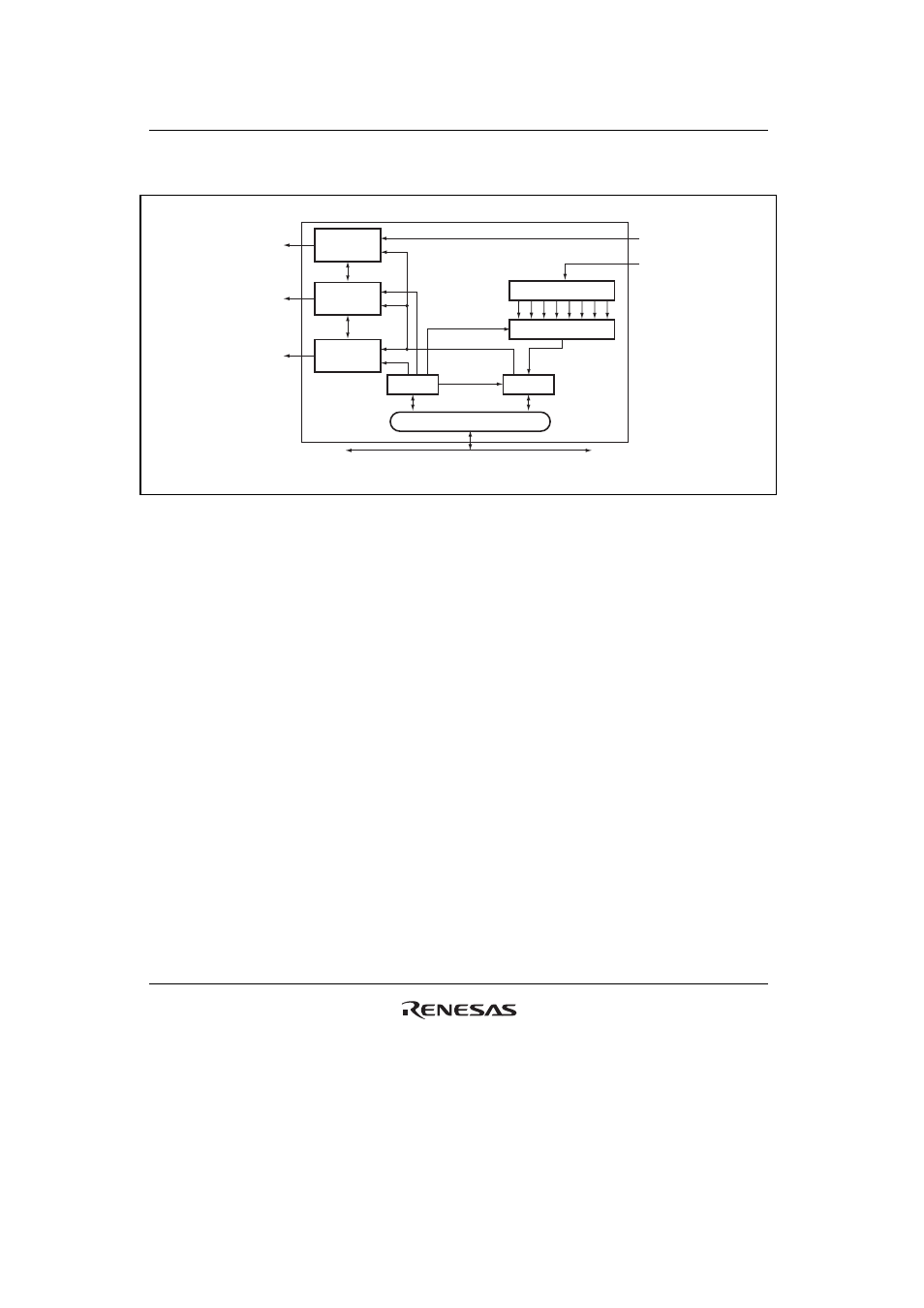

Figure 5.1 shows a block diagram of the WDT.

WTCSR

Standby

control

Bus interface

WTCNT

Divider

Clock selector

Clock

Standby

mode

Peripheral

clock

Standby

cancellation

Reset

control

Clock selection

WDT

Overflow

Internal

reset

request

Interrupt

control

Interrupt

request

[Legend]

WTCSR:

WTCNT:

Watchdog timer control/status register

Watchdog timer counter

Figure 5.1 Block Diagram of the WDT

5.2 Register

Descriptions

The WDT has the following two registers. See section 24, List of Registers, for the addresses and

access sizes of these registers.

• Watchdog timer counter (WTCNT)

• Watchdog timer control/status register (WTCSR)

5.2.1

Watchdog Timer Counter (WTCNT)

The watchdog timer counter (WTCNT) is an 8-bit readable/writable register that is incremented by

cycles of the selected clock signal. When an overflow occurs, it generates a reset in watchdog

timer mode and an interrupt in interval timer mode. The WTCNT counter is initialized to H'00

only by a power-on reset caused by the

RESETP pin. Use a word access to write to the WTCNT

counter, writing H'5A in the upper byte. Use a byte access to read the WTCNT.

Note: The WTCNT differs from other registers in the prevention of erroneous writes.

See section 5.2.3, Notes on Register Access, for details.