Renesas SH7641 User Manual

Page 732

Section 18 Multi-Function Timer Pulse Unit (MTU)

Rev. 4.00 Sep. 14, 2005 Page 682 of 982

REJ09B0023-0400

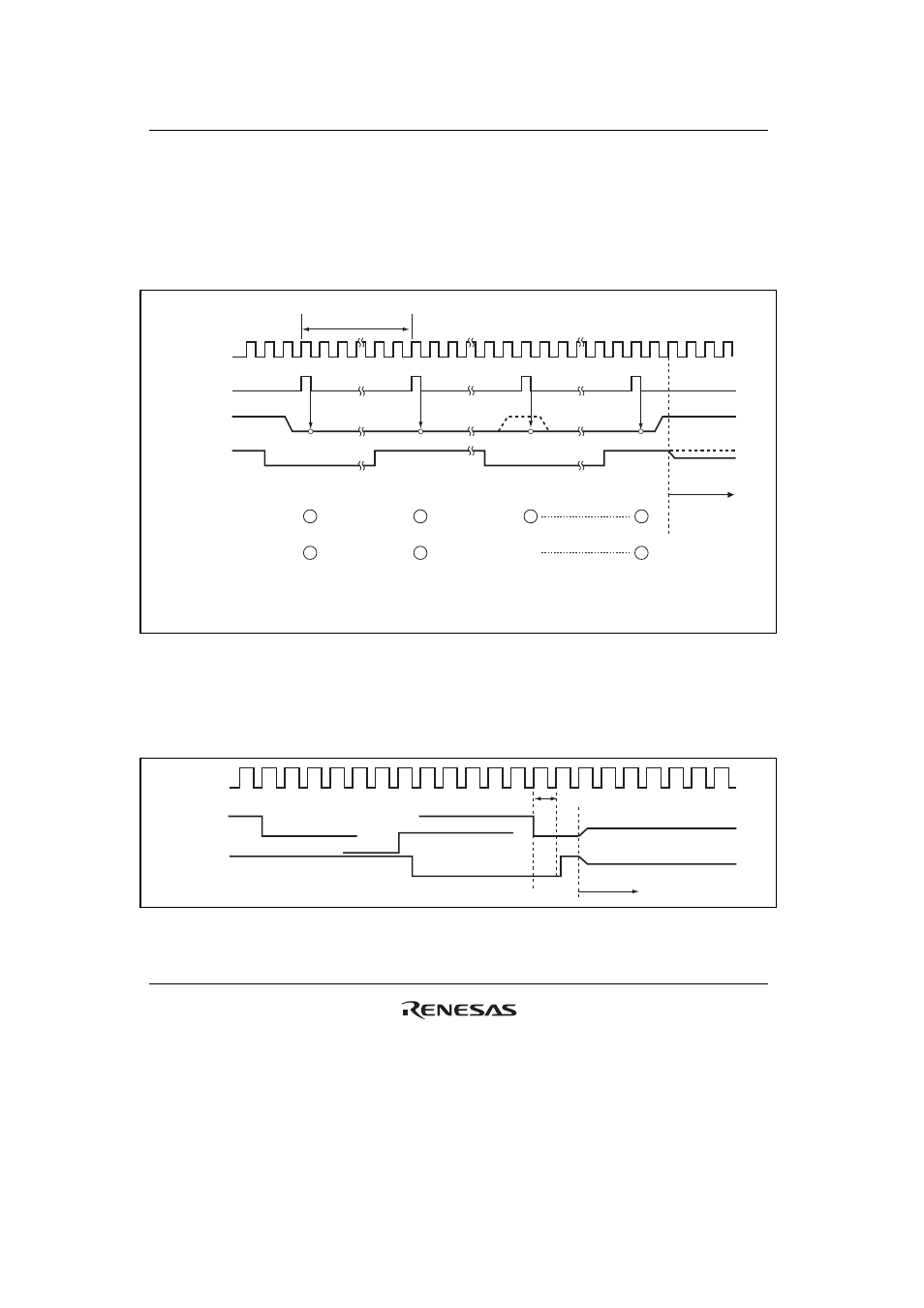

2. Low-Level Detection

Figure 18.116 shows the low-level detection operation. Sixteen continuous low levels are

sampled with the sampling clock established by the ICSR1. If even one high level is detected

during this interval, the low level is not accepted.

Furthermore, the timing when the large-current pins enter the high-impedance state from the

sampling clock is the same in both falling-edge detection and in low-level detection.

P

φ

Sampling

clock

3

POE input

TIOC3B/

PTE[6]

When low level is

sampled at all points

When high level is

sampled at least once

Flag set

(

POE received)

Flag not set

Hi-Z state*

Note: *

Other high-current pins (TIOC3D/PTE[4], TIOC4A/PTE[3], TIOC4B/PTE[2], TIOC4C/PTE[1],

and TIOC4D/PTE[0]) also become the Hi-Z state at the same timing.

2

1

2

1

16

13

8/16/128 clock

cycles

Figure 18.116 Low-Level Detection Operation

Output-Level Compare Operation: Figure 18.117 shows an example of the output-level

compare operation for the combination of TIOC3B/PTE[6] and TIOC3D/PTE[4]. The operation is

the same for the other pin combinations.

P

φ

TIOC3D/

PTE[4]

TIOC3B/

PTE[6]

0 level overlapping detected

Hi-Z

Figure 18.117 Output-Level Detection Operation