Renesas SH7641 User Manual

Page 282

Section 10 Interrupt Controller (INTC)

Rev. 4.00 Sep. 14, 2005 Page 232 of 982

REJ09B0023-0400

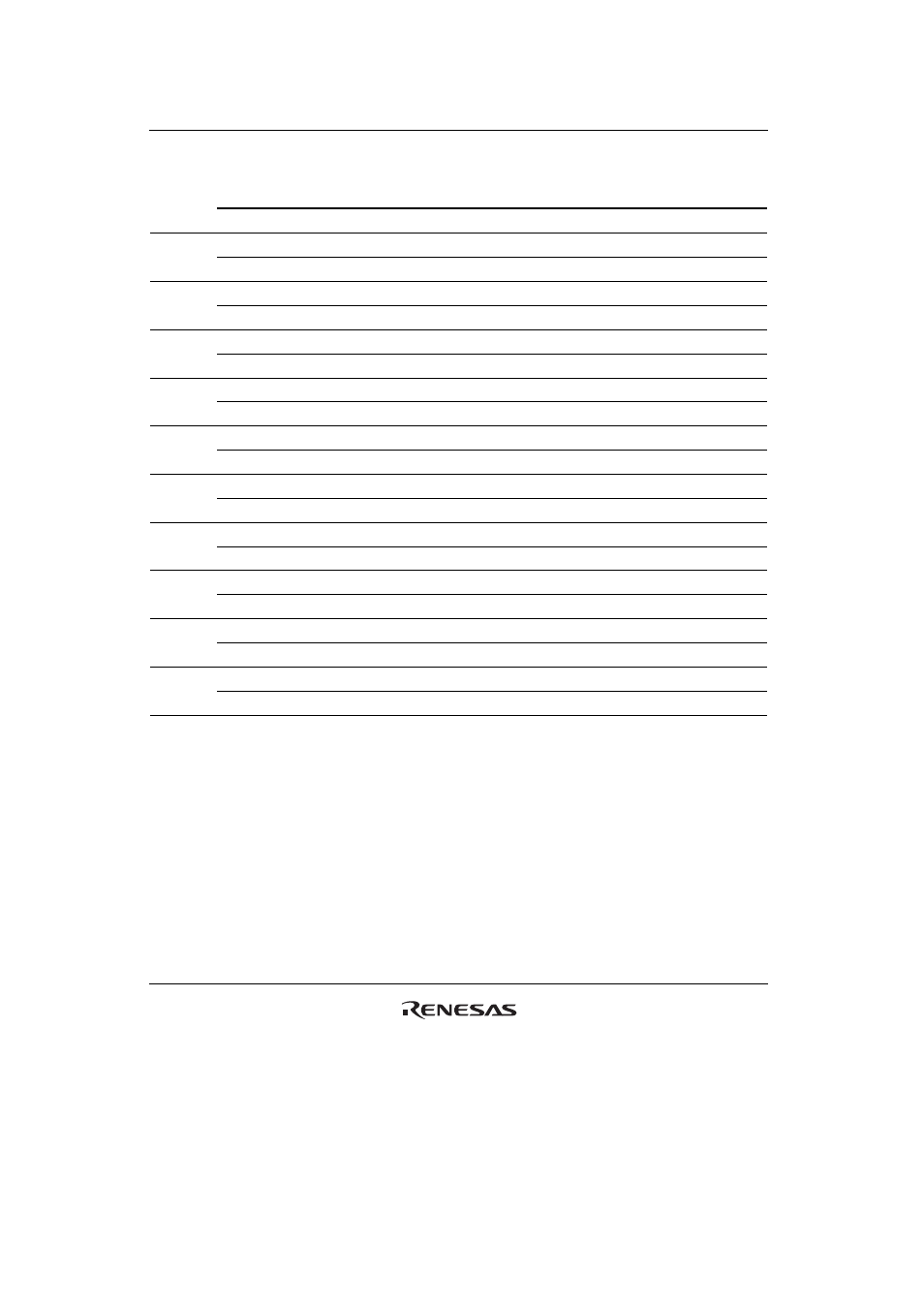

Table 10.4 Correspondence between Interrupt Sources and IMCR0 to IMCR10

Bit Name (Function Name)

Register

Name

7 6 5 4 3 2 1 0

IMCR0

IRQ7 IRQ6 IRQ5 IRQ4 IRQ3 IRQ2 IRQ1 IRQ0

(IRQ) (IRQ) (IRQ) (IRQ) (IRQ) (IRQ) (IRQ) (IRQ)

IMCR1 TxI0

BRI0

RxI0

ERI0 DEI3 DEI2 DEI1 DEI0

(SCIF0) (SCIF0) (SCIF0) (SCIF0) (DMAC) (DMAC) (DMAC) (DMAC)

IMCR2

— — ADI0

TxI1

BRI1

RxI1

ERI1

(ADC0) (ADC0) (ADC0) (ADC0) (SCIF1) (SCIF1) (SCIF1) (SCIF1)

IMCR4

— — — — ITI — — —

— — — — (WDT)

(WDT)

(WDT)

(WDT)

IMCR5 TxI2

BRI2

RxI2

ERI2 ADI1 USIHP

USI1 USI0

(SCIF2) (SCIF2) (SCIF2) (SCIF2) (ADC1) (USB) (USB) (USB)

IMCR6 TCI2U TCI2V TGI2B TGI2A TCI1U TCI1V TGI1B TGI1A

(MTU2) (MTU2) (MTU2) (MTU2) (MTU1) (MTU1) (MTU1) (MTU1)

IMCR7

— — — TCI0V

TGI0D

TGI0C

TGI0B

TGI0A

(MTU0) (MTU0) (MTU0) (MTU0) (MTU0) (MTU0) (MTU0) (MTU0)

IMCR8

— — — TCI3V

TGI3D

TGI3C

TGI3B

TGI3A

(MTU3) (MTU3) (MTU3) (MTU3) (MTU3) (MTU3) (MTU3) (MTU3)

IMCR9

— — — TCI4V

TGI4D

TGI4C

TGI4B

TGI4A

(MTU4) (MTU4) (MTU4) (MTU4) (MTU4) (MTU4) (MTU4) (MTU4)

IMCR10

— — CMI1

CMI0

IIC2I

— — OEI

(CMT) (CMT) (CMT) (CMT) (IIC2) (IIC2) (POE) (POE)

Note:

: Reserved: These bits are always read as 0. The write value should always be 0.