12 h-udi related pin timing, Q = 3.0 v to 3.6 v, v, 8 v ± 5%, av – Renesas SH7641 User Manual

Page 1010: 0 v to 3.6 v, v, Q = av, Figure 25.51 tck input timing

Section 25 Electrical Characteristics

Rev. 4.00 Sep. 14, 2005 Page 960 of 982

REJ09B0023-0400

25.3.12 H-UDI Related Pin Timing

Table 25.13 H-UDI Related Pin Timing

Conditions: V

CC

Q = 3.0 V to 3.6 V, V

CC

= 1.8 V

± 5%, AV

CC

= 3.0 V to 3.6 V,

V

SS

= V

SS

Q = AV

SS

= 0 V, Ta =

−40°C to +85°C

Item Symbol

Min.

Max.

Unit

Figure(s)

TCK cycle time

t

TCKcyc

50

—

ns

25.51

TCK high pulse width

t

TCKH

0.4 0.6 tTckcyc

TCK low pulse width

t

TCKL

0.4 0.6 tTckcyc

TRST setup time

t

TRSTS

20 — ns 25.52

TRST hold time

t

TRSTH

50 —

t

cyc

TDI setup time

t

TDIS

10 — ns 25.53

TDI hold time

t

TDIH

10 — ns

TMS setup time

t

TMSS

10 — ns

TMS hold time

t

TMSH

10 — ns

TDO delay time

t

TDOD

— 20 ns

Capture register setup

time

t

CAPTS

10 —

ns 25.54

Capture register hold

time

t

CAPTH

10 —

ns

Update register delay

time

t

UPDTED

—

16

ns

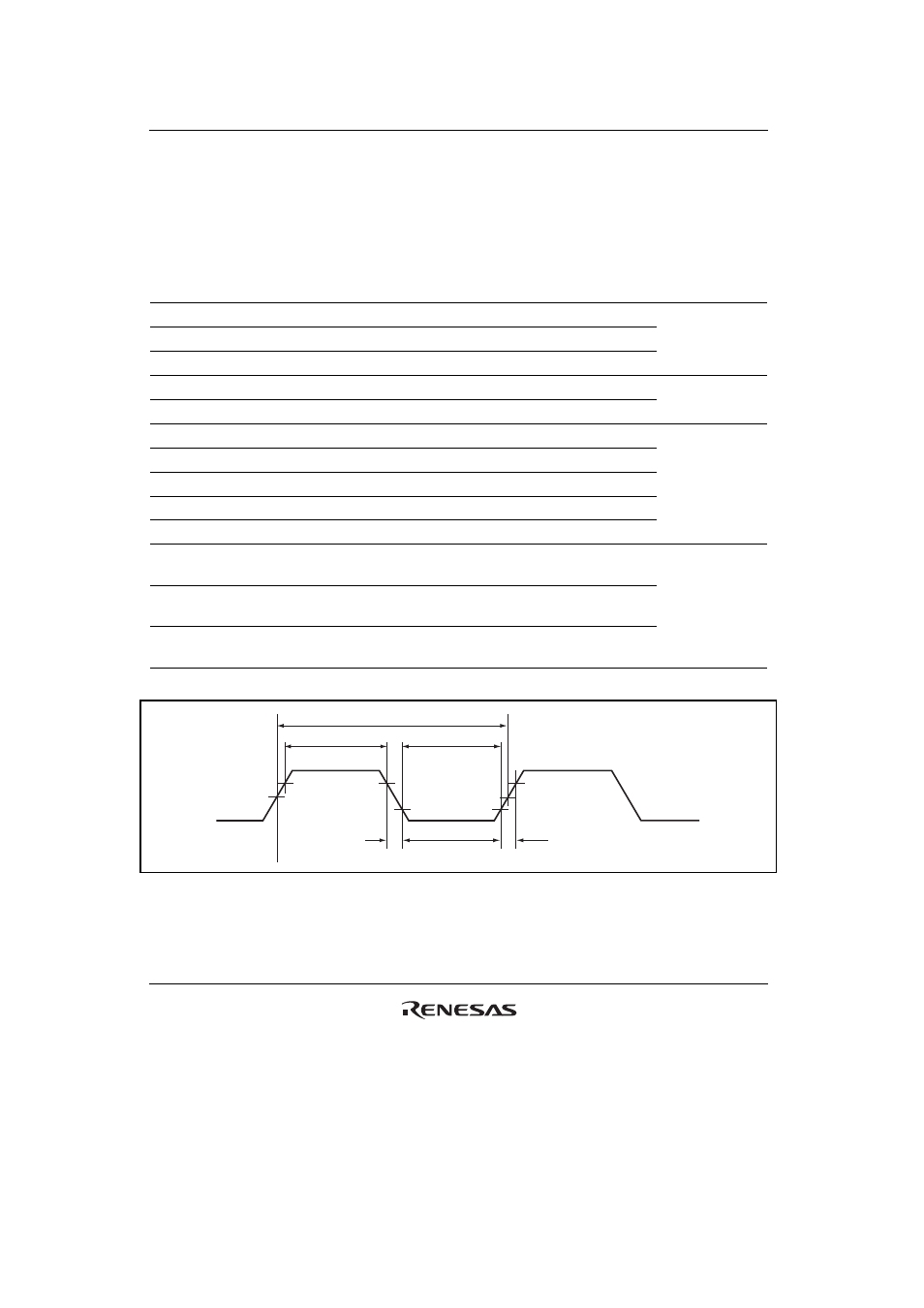

t

TCKcyc

V

IH

1/2 V

cc

Q

1/2 V

cc

Q

V

IH

V

IL

V

IL

V

IH

t

TCKL

t

TCKF

t

TCKF

t

TCKH

Figure 25.51 TCK Input Timing