Renesas SH7641 User Manual

Page 489

Section 13 Direct Memory Access Controller (DMAC)

Rev. 4.00 Sep. 14, 2005 Page 439 of 982

REJ09B0023-0400

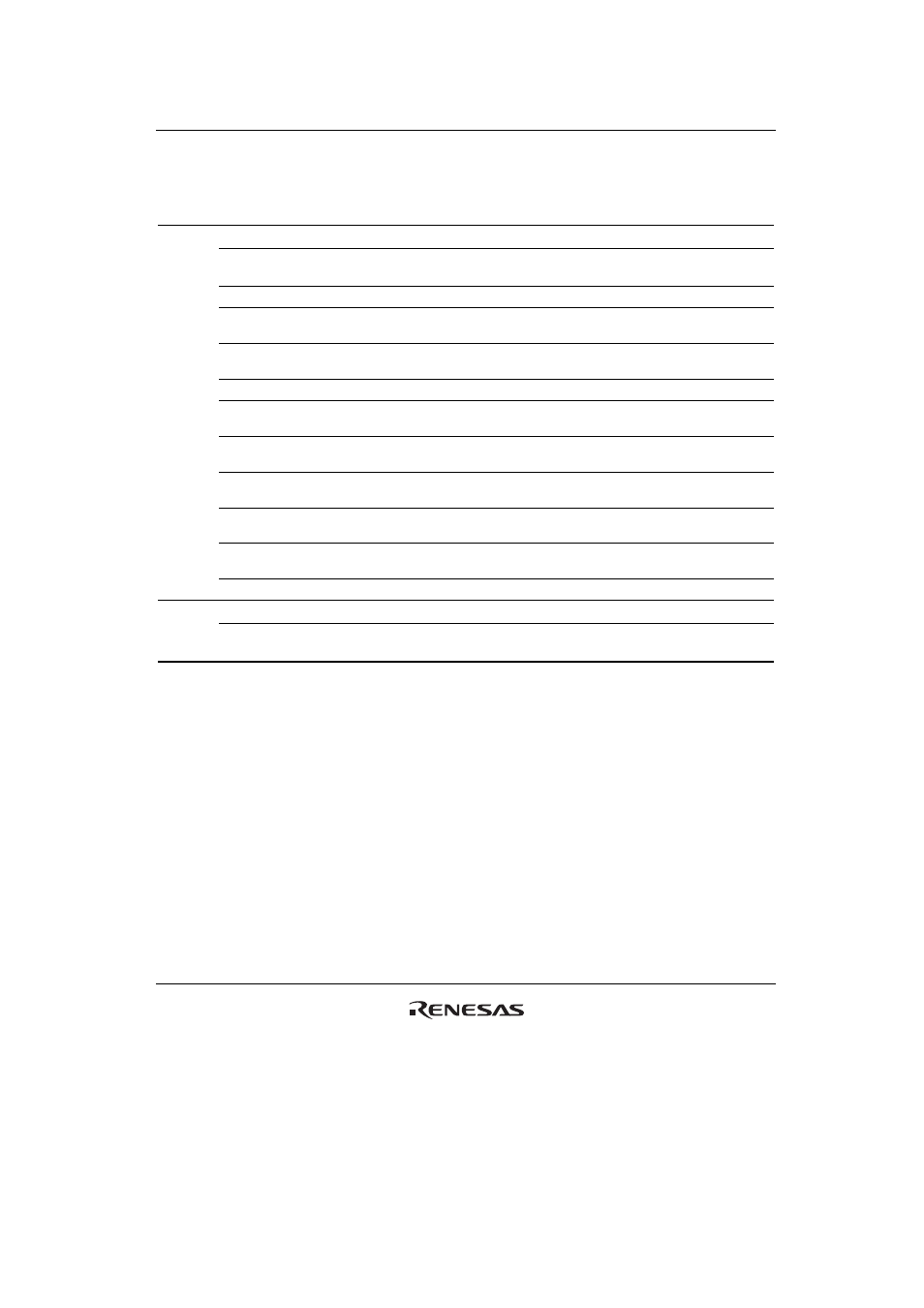

Table 13.9 Relationship of Request Modes and Bus Modes by DMA Transfer Category

Address

Mode Transfer

Category

Request

Mode

Bus

Mode

Transfer

Size (Bits)

Usable

Channels

External device with

DACK and external memory External B/C 8/16/32/128 0,

1

External device with

DACK and memory-mapped

external device

External B/C 8/16/32/128 0,

1

External memory and external memory

All*

1

B/C

8/16/32/128

0 to 3*

5

External memory and memory-mapped external

device

All*

1

B/C

8/16/32/128

0 to 3*

5

Memory-mapped external device and memory-

mapped external device

All*

1

B/C

8/16/32/128

0 to 3*

5

External memory and on-chip peripheral module

All*

2

B/C*

3

8/16/32/128*

4

0 to 3*

5

Memory-mapped external device and

on-chip peripheral module

All*

2

B/C*

3

8/16/32/128*

4

0 to 3*

5

On-chip peripheral module and on-chip peripheral

module

All*

2

B/C*

3

8/16/32/128*

4

0 to 3*

5

X/Y memory, U memory and X/Y memory,

U memory

All*

1

B/C

8/16/32/128

0 to 3*

5

X/Y memory, U memory and memory-mapped

external device

All*

1

B/C

8/16/32/128

0 to 3*

5

X/Y memory, U memory and on-chip peripheral

module

All*

2

B/C*

3

8/16/32/128*

4

0 to 3*

5

Dual

X/Y memory, U memory and external memory

All*

1

B/C

8/16/32/128

0 to 3*

5

External device with

DACK and external memory External B/C 8/16/32/128 0,

1

Single

External device with

DACK and memory-mapped

external device

External B/C 8/16/32/128 0,

1

[Legend]

B: Burst

C: Cycle steal

Notes: 1. External requests, auto requests, and on-chip peripheral module requests are all

available. In the case of on-chip peripheral module requests, however, CMT0, CMT1,

and MTU0 to MTU4 are only available.

2. External requests, auto requests, and on-chip peripheral module requests are all

available. However, for on-chip peripheral module requests, the module must be

designated as the transfer request source or the transfer destination except CMT0,

CMT1, and MTU0 to MTU4.

3. For on-chip peripheral module requests, the transfer source is in cycle steal mode

except CMT0, CMT1, and MTU0 to MTU4.

4. Access size permitted for the on-chip peripheral module register functioning as the

transfer source or transfer destination.

5. If the transfer request is an external request, channels 0 to 1 are only available.