Renesas SH7641 User Manual

Page 425

Section 12 Bus State Controller (BSC)

Rev. 4.00 Sep. 14, 2005 Page 375 of 982

REJ09B0023-0400

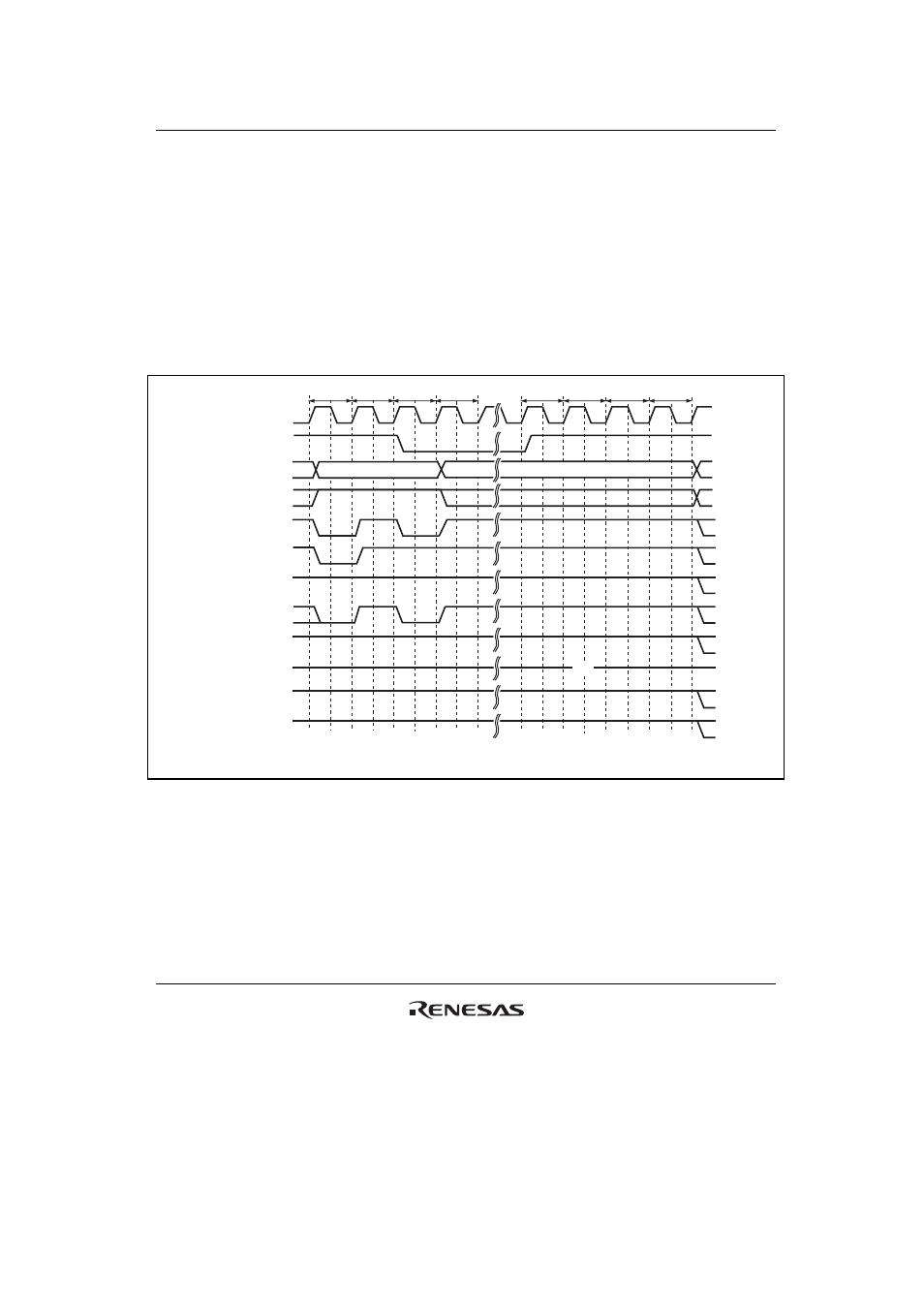

• Deep power-down mode

The low-power SDRAM supports the deep power-down mode as a low-power consumption

mode. In the partial self-refresh function, self-refresh is performed on a specific area. In the

deep power-down mode, self-refresh will not be performed on any memory area. This mode is

effective in systems where all of the system memory areas are used as work areas.

If the RMODE bit in the SDCR is set to 1 while the DEEP and RFSH bits in the SDCR are set to

1, the low-power SDRAM enters the deep power-down mode. If the RMODE bit is cleared to 0,

the CKE signal is pulled high to cancel the deep power-down mode. Before executing an access

after returning from the deep power-down mode, the power-up sequence must be re-executed.

Tpw

Tp

Tdpd

Trc

Hi-Z

Trc

Trc

Trc

Trc

CKIO

CKE

A25 to A0

CSn

RD/

WR

RASL, RASU

DQMxx

D31 to D0

BS

DACKn*

2

A12/A11*

1

CASL, CASU

Notes: 1. Address pin to be connected to pin A10 of SDRAM.

2. The waveform for

DACKn is when active low is specified.

Figure 12.35 Deep Power-Down Mode Transition Timing