3 boundary scan register (sdbsr) – Renesas SH7641 User Manual

Page 508

Section 15 User Debugging Interface (H-UDI)

Rev. 4.00 Sep. 14, 2005 Page 458 of 982

REJ09B0023-0400

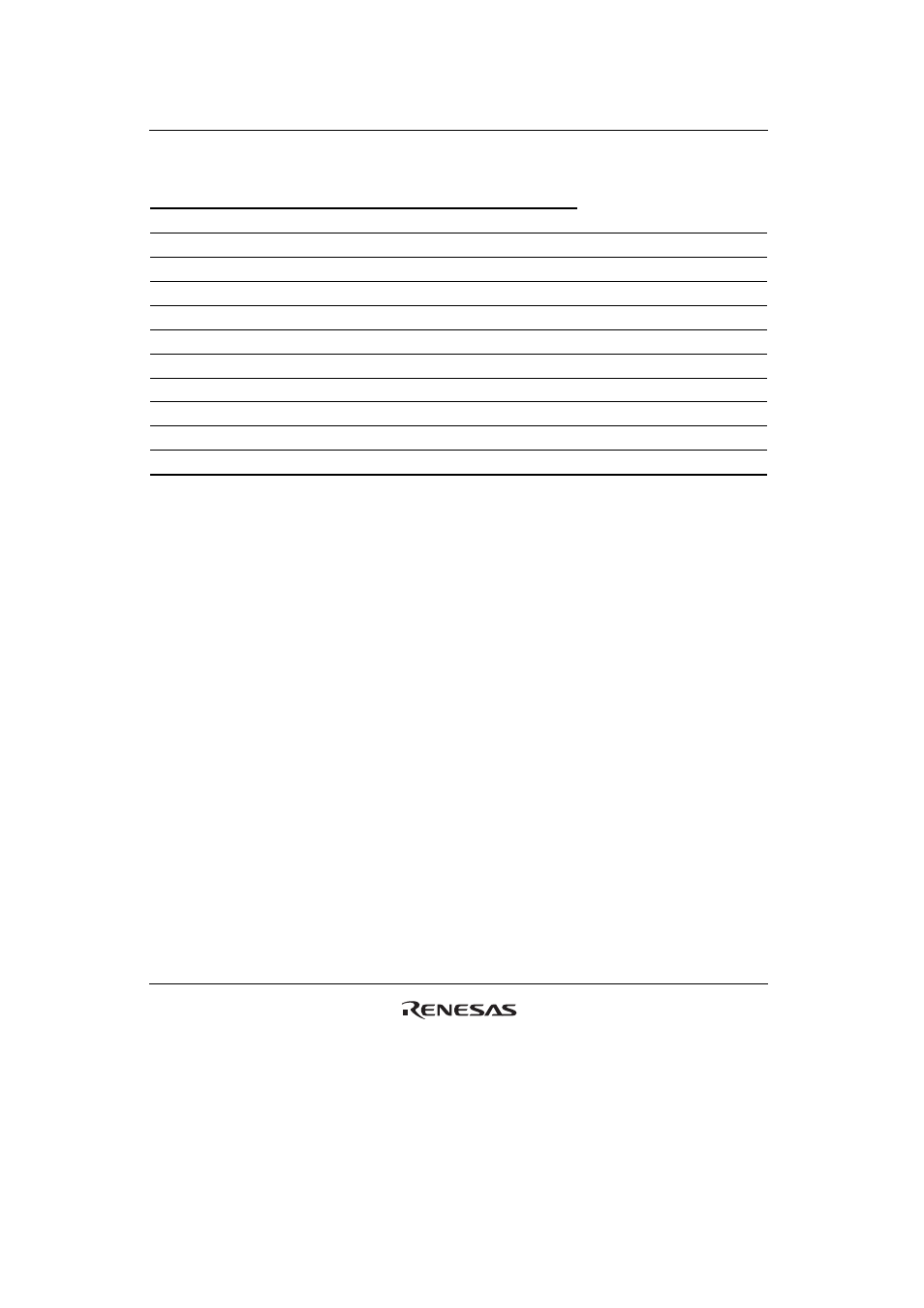

Table 15.2 H-UDI Commands

Bits 15 to 8

TI7 TI6 TI5 TI4 TI3 TI2 TI1 TI0 Description

0 0 0 0 — — — — JTAG

EXTEST

0 0 1 0 — — — — JTAG

CLAMP

0 0 1 1 — — — — JTAG

HIGHZ

0 1 0 0 — — — — JTAG

SAMPLE/PRELOAD

0 1 1 0 — — — — H-UDI

reset

negate

0 1 1 1 — — — — H-UDI

reset

assert

1 0 1 — — — — — H-UDI

interrupt

1 1 1 0 — — — — JTAG

IDCODE

(Initial

value)

1 1 1 1 — — — — JTAG

BYPASS

Other than the above

Reserved

15.3.3

Boundary Scan Register (SDBSR)

SDBSR is a 469-bit shift register, located on the PAD, for controlling the input/output pins of this

LSI.

Using the EXTEST, SAMPLE/PRELOAD, CLAMP, and HIGHZ commands, a boundary scan

test conforming to the JTAG standard can be carried out. Table 15.3 shows the correspondence

between this LSI's pins and boundary scan register bits.