Renesas SH7641 User Manual

Page 440

Section 12 Bus State Controller (BSC)

Rev. 4.00 Sep. 14, 2005 Page 390 of 982

REJ09B0023-0400

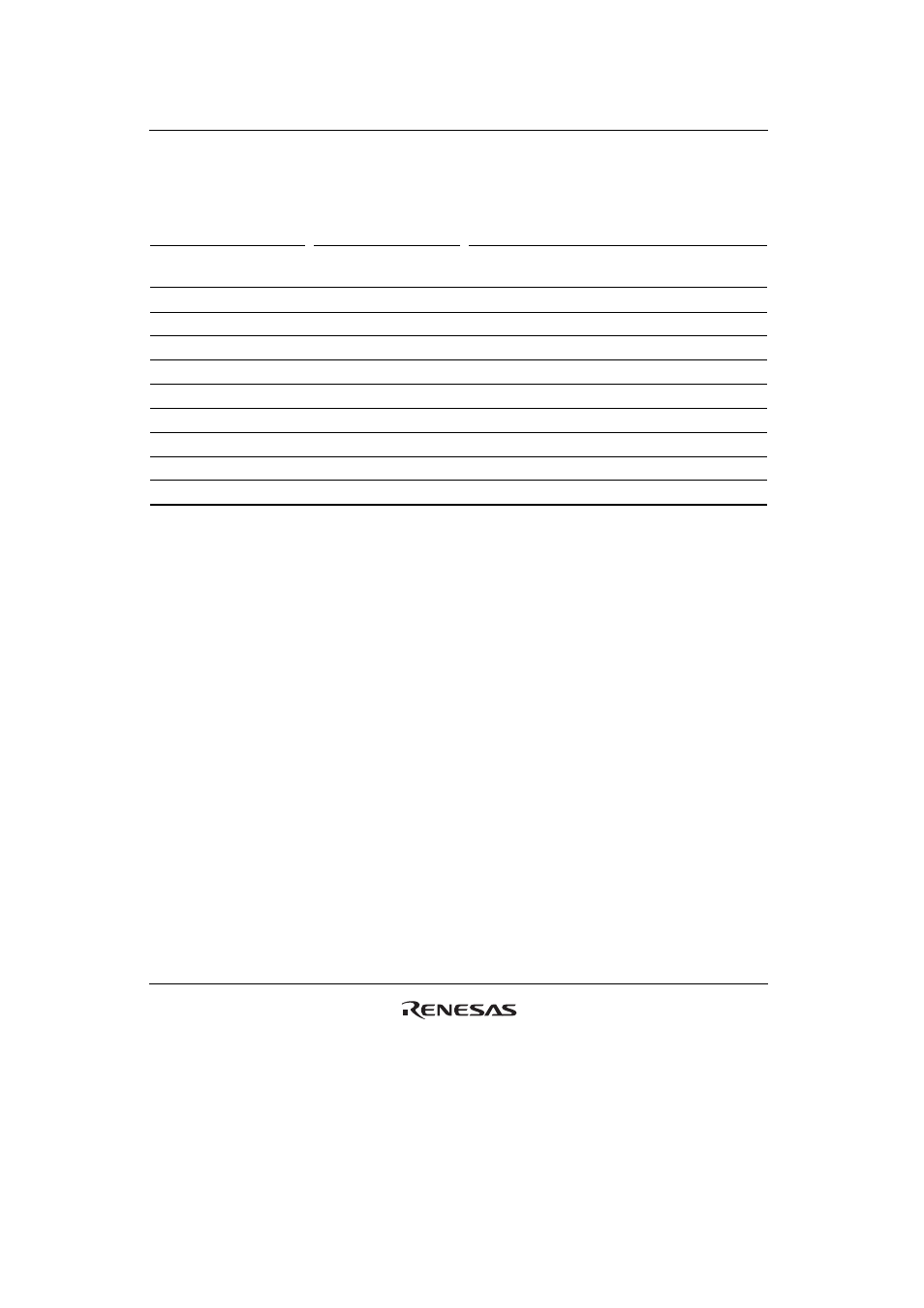

Table 12.19 Minimum Number of Idle Cycles between Access Cycles during DMAC Dual

Address Mode Transfer for the Normal Space Interface

BSC Register Setting

When Access Size is

Less than Bus Width

When Access Size Exceeds Bus Width

CSnWCR.

WM Setting

CSnBCR

Idle Setting

Read to

Write

Write to

Read

Continuous

Read

*

1

Read to

Write

*

2

Continuous

Write

*

1

Write to

Read

*

2

1 0 2 0 0 2 0 0

0 0 2 1 1 2 1 1

1 1 2 1 1 2 1 1

0 1 2 1 1 2 1 1

1 2 2 2 2 2 2 2

0 2 2 2 2 2 2 2

1 4 4 4 4 4 4 4

0 4 4 4 4 4 4 4

0, 1

n (n

≥6)

n n n n n n

Notes:

DMAC is operated by B

φ. The minimum number of idle cycles is not affected by

changing a clock ratio.

1. Minimum number of idle cycles between the upper and lower 16-bit access cycles in the

32-bit access cycle when the bus width is 16 bits, and the minimum number of idle

cycles between continuous access cycles during 16-byte transfer

2. Minimum number of idle cycles for other than the above cases.