4 csn assert period expansion – Renesas SH7641 User Manual

Page 381

Section 12 Bus State Controller (BSC)

Rev. 4.00 Sep. 14, 2005 Page 331 of 982

REJ09B0023-0400

12.5.4

CSn Assert Period Expansion

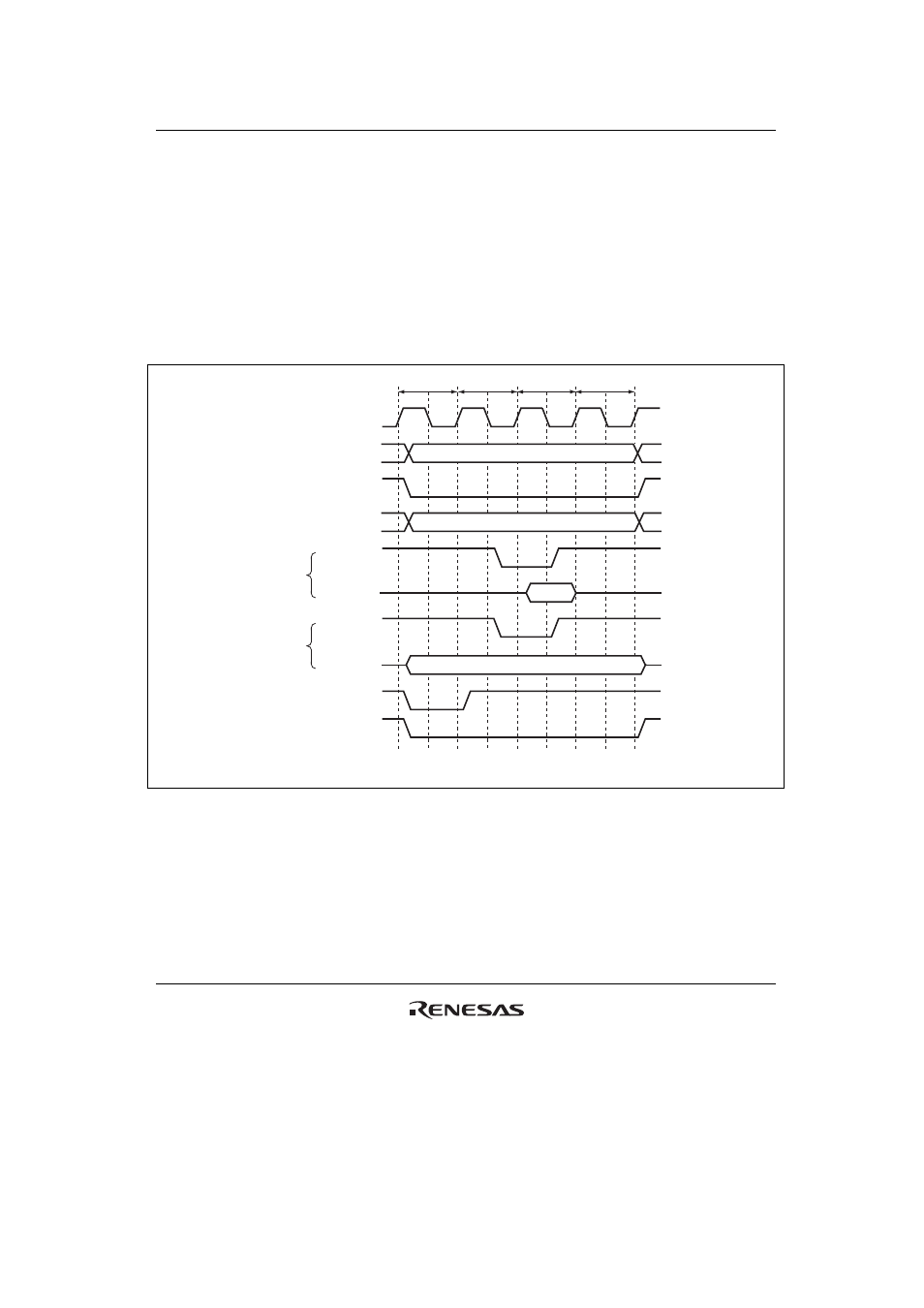

The number of cycles from

CSn assertion to RD, WEn assertion can be specified by setting bits

SW1 and SW0 in CSnWCR. The number of cycles from

RD, WEn negation to CSn negation can

be specified by setting bits HW1 and HW0. Therefore, a flexible interface to an external device

can be obtained. Figure 12.11 shows an example. A Th cycle and a Tf cycle are added before and

after an ordinary cycle, respectively. In these cycles,

RD and WEn are not asserted, while other

signals are asserted. The data output is prolonged to the Tf cycle, and this prolongation is useful

for devices with slow writing operations.

T1

CKIO

A25 to A0

CSn

RD/

WR

RD

D31 to D0

WEn

D31 to D0

BS

Th

Read

Write

T2

DACKn*

Tf

Note: * The waveform for

DACKn is when active low is specified.

Figure 12.11

CSn Assert Period Expansion