Renesas SH7641 User Manual

Page 796

Section 19 Serial Communication Interface with FIFO (SCIF)

Rev. 4.00 Sep. 14, 2005 Page 746 of 982

REJ09B0023-0400

6. When Using the DMAC

Using an External Clock in Chock Synchronous Mode:

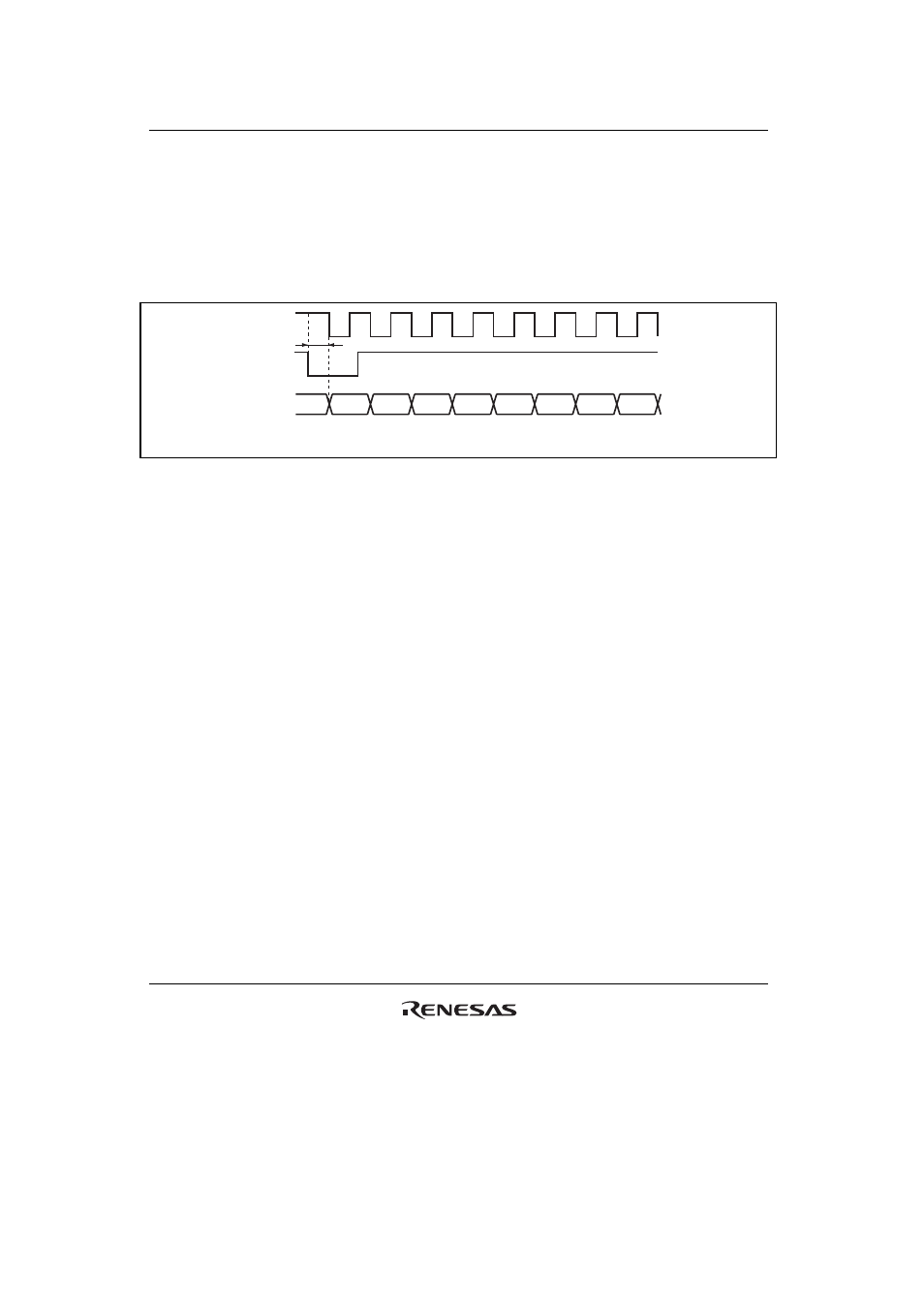

When using an external clock as the synchronization clock, after SCFTDR is updated by

the DMAC, an external clock should be input after at least five peripheral clock cycles. A

malfunction may occur when the transfer clock is input within four cycles after updating

SCFTDR (figure 19.20).

SCK

TDRE

TxD

D0

D1

D2

D6

D7

D3

D4

D5

t

Note: When the SCIF is operated on an external clock, set t > 4.

Figure 19.20 DMA Transfer Example in the Synchronization Clock

DMA Transfer Request:

When a DMA transfer is requested from the SCIF of which transfer request is allowed by

the DMAC, the transfer request from the SCIF is held in the DMAC. This transfer request

is cleared after it is actually transferred.

Even if the DME bit of the DMA operation register (DMAOR) and the DE bit of the DMA

channel control register (CHCR) are cleared, the DMA transfer request from the SCIF is

retained. In this state, note that the DMA transfer is done for one time without any DMA

transfer request from the SCIF when the DMAC allows the transfer request from the SCIF.

TEND Flag:

When the transmit FIFO data empty DMA transfer request is generated and the transmit

data is written to SCFTDR by the DMAC, the value indicated by the TEND flag is

undefined. Thus, do not use the TEND flag as a transmit end flag.