Renesas SH7641 User Manual

Page 274

Section 10 Interrupt Controller (INTC)

Rev. 4.00 Sep. 14, 2005 Page 224 of 982

REJ09B0023-0400

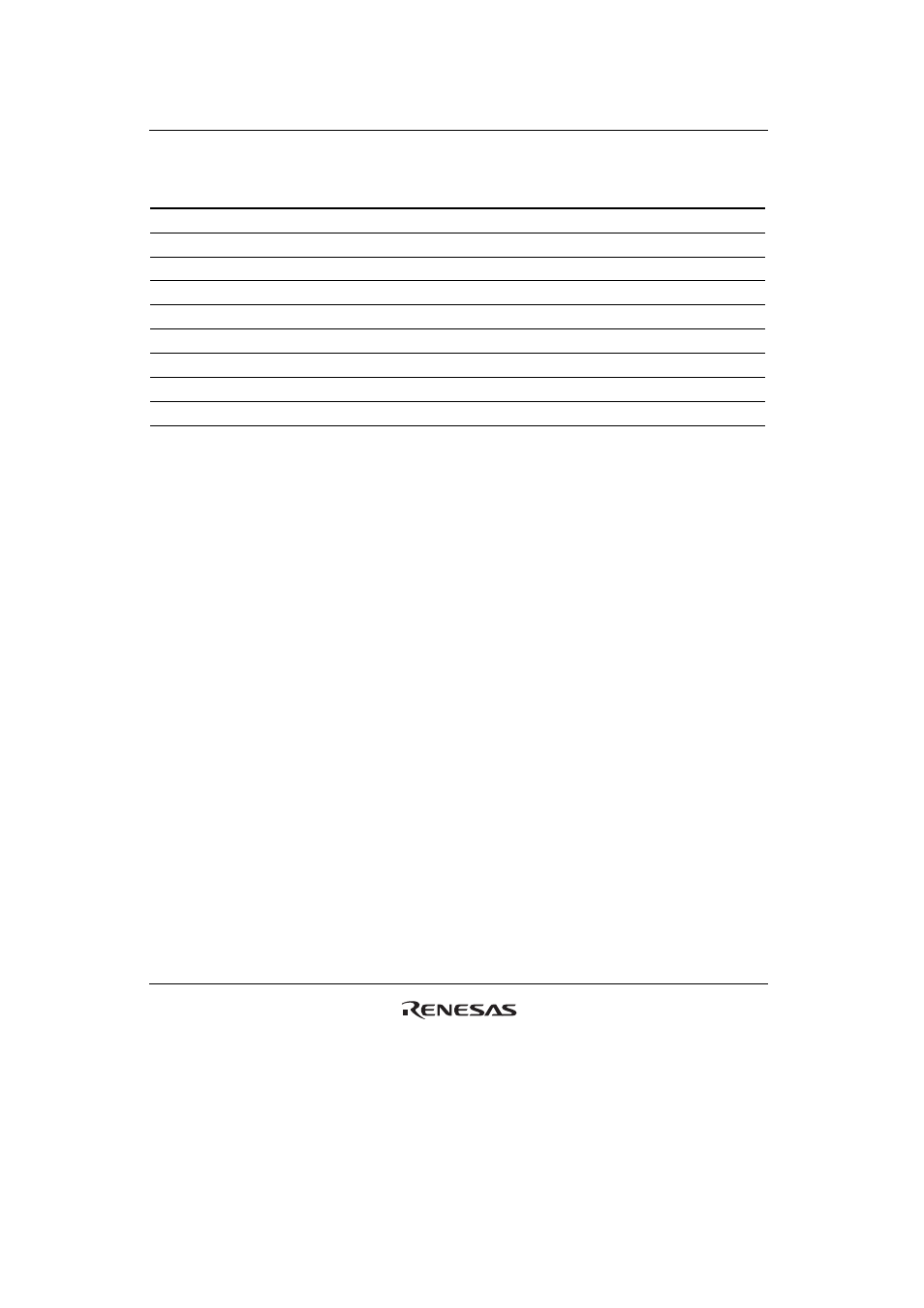

Table 10.2 Interrupt Sources and IPRB to IPRJ

Register

Bits 15 to 12

Bits 11 to 8

Bits 7 to 4

Bits 3 to 0

IPRB WDT Reserved* Reserved* Reserved*

IPRC IRQ3 IRQ2 IRQ1 IRQ0

IPRD IRQ7 IRQ6 IRQ5 IRQ4

IPRE Reserved*

SCIF0 SCIF1 ADC0

IPRF ADC1 SCIF2

USB CMT

IPRG

MTU0 (A/B/C/D)

MTU0 (V)

MTU1 (A/B)

MTU1 (V/U)

IPRH

MTU2 (A/B)

MTU2 (V/U)

MTU3 (A/B/C/D)

MTU3 (V)

IPRI

MTU4 (A/B/C/D)

MTU4 (V)

POE

IIC2

IPRJ

DMAC0 DMAC1 DMAC2 DMAC3

Note: * Reserved: These bits are always read as 0. The write value should always be 0.

As shown in table 10.2, on-chip peripheral module or IRQ interrupts are assigned to four 4-bit

groups in each register. These 4-bit groups (bits 15 to 12, bits 11 to 8, bits 7 to 4, and bits 3 to 0)

are set with values from H'0 (0000) to H'F (1111). Setting of H'0 means priority level 0 (masking

is requested); H'F means priority level 15 (the highest level).