Renesas SH7641 User Manual

Page 497

Section 13 Direct Memory Access Controller (DMAC)

Rev. 4.00 Sep. 14, 2005 Page 447 of 982

REJ09B0023-0400

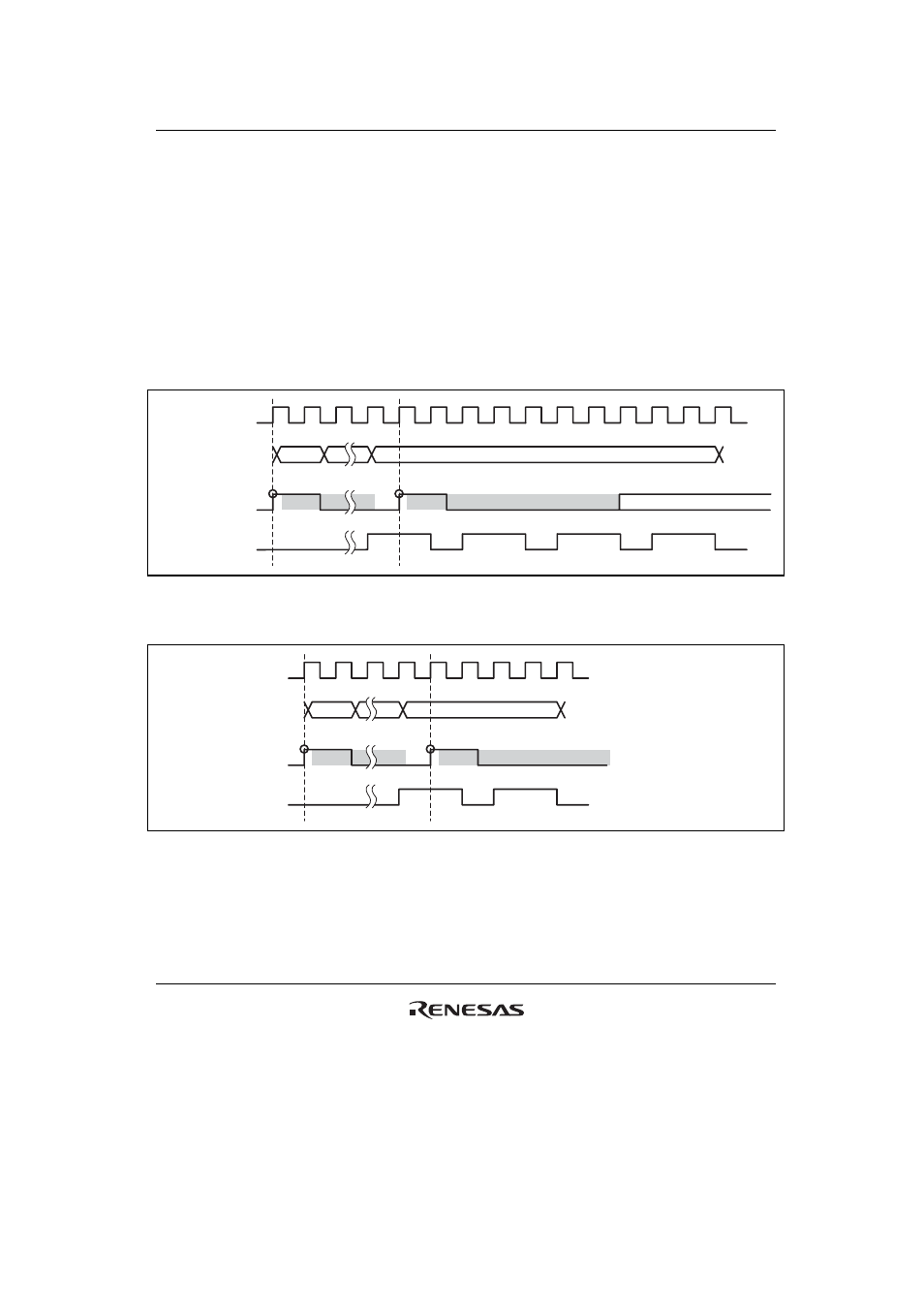

• Idle cycles between read-read cycles in the same spaces (IWRRS = 01 or more)

• External wait mask specification (WM = 0).

In addition to the above conditions, the following conditions are included depending on the

detection method of DREQ.

• For DREQ level detection: only write access

• For DREQ edge detection: both write access and read access

Phenomenon: The detection timings of the DREQ pin in the above access are shown in figures

13.19 to 13.22.

CKIO

CPU

DMAC write or read

Bus cycle

Non-sensitive period

1st acceptance

2nd acceptance

3rd acceptance possible

Non-sensitive period

DREQ

(Rising edge)

DACK

(High-active)

Figure 13.19 Example of DREQ Input Detection in Cycle Steal Mode Edge Detection

When DACK is Divided to 4 by Idle Cycles

CPU

DMAC write or read

Non-sensitive period

1st acceptance

2nd acceptance

3rd acceptance is after the

next DACK assertion

Non-sensitive period

CKIO

Bus cycle

DREQ

(Rising edge)

DACK

(High-active)

Figure 13.20 Example of DREQ Input Detection in Cycle Steal Mode Edge Detection

When DACK is Divided to 2 by Idle Cycles