Renesas SH7641 User Manual

Page 689

Section 18 Multi-Function Timer Pulse Unit (MTU)

Rev. 4.00 Sep. 14, 2005 Page 639 of 982

REJ09B0023-0400

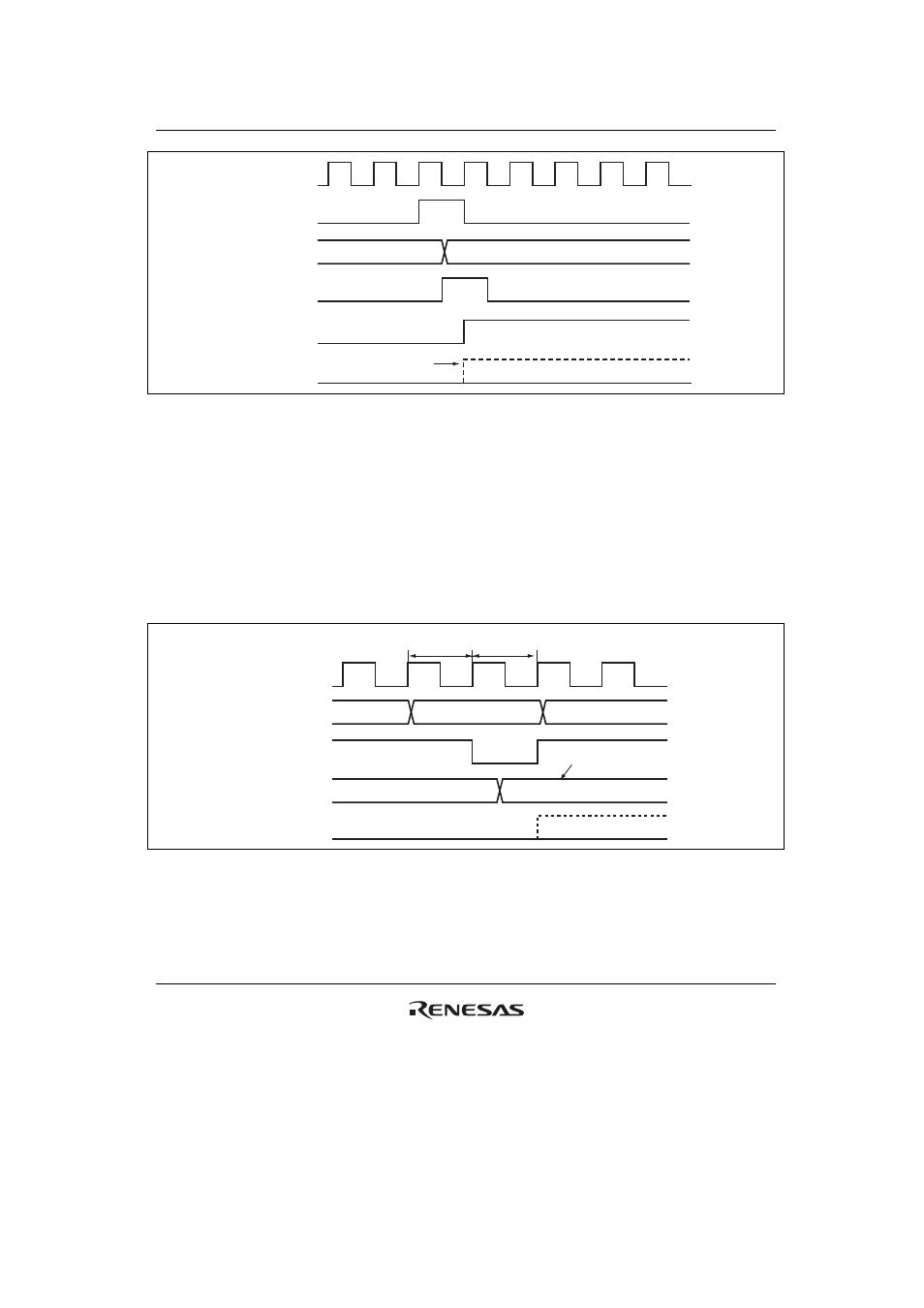

Counter clear

signal

TCNT

TCNT input

clock

P

φ

H'FFFF

H'0000

TGF

TCFV

Disabled

Figure 18.83 Conflict between Overflow and Counter Clearing

18.7.17 Conflict

between

TCNT

Write and Overflow/Underflow

If there is an up-count or down-count in the T2 state of a TCNT write cycle, and

overflow/underflow occurs, the TCNT write takes precedence and the TCFV/TCFU flag in TSR is

not set.

Figure 18.84 shows the operation timing when there is conflict between TCNT write and

overflow.

Write signal

Address

P

φ

TCNT address

TCNT

TCNT write cycle

T1

T2

H'FFFF

M

TCNT write data

TCFV flag

Figure 18.84 Conflict between TCNT Write and Overflow

This manual is related to the following products: