3 cpu instruction formats – Renesas SH7641 User Manual

Page 108

Section 2 CPU

Rev. 4.00 Sep. 14, 2005 Page 58 of 982

REJ09B0023-0400

2.4.3 CPU

Instruction

Formats

Table 2.13 shows the instruction formats, and the meaning of the source and destination operands,

for instructions executed by the CPU core. The meaning of the operands depends on the

instruction code. The following symbols are used in the table.

xxxx: Instruction

code

mmmm: Source register

nnnn: Destination

register

iiii: Immediate

data

dddd: Displacement

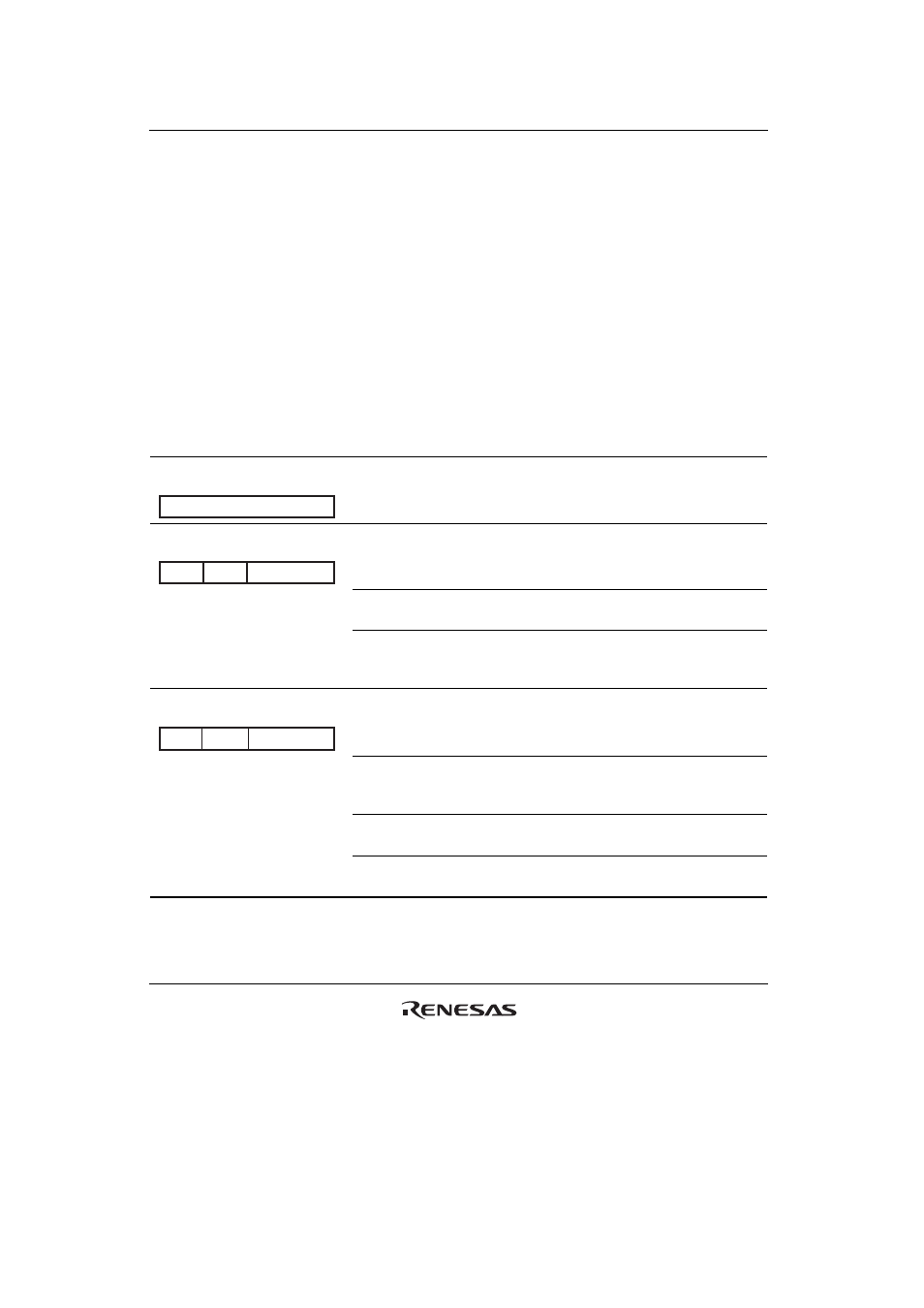

Table 2.13 CPU Instruction Formats

Instruction Format

Source

Operand

Destination

Operand Sample

Instruction

0 type

xxxx

xxxx

xxxx

xxxx

15

0

NOP

n type

xxxx

xxxx

xxxx

nnnn

15

0

nnnn

: register

direct

MOV T Rn

Control register or

system register

nnnn

: register

direct

STS MACH,Rn

Control register or

system register

nnnn

: pre-

decrement register

indirect

STC.L SR,@-Rn

m type

xxxx

mmmm

xxxx

xxxx

15

0

mmmm

: register

direct

Control register or

system register

LDC Rm,SR

mmmm

: post-

increment register

indirect

Control register or

system register

LDC.L @Rm+,SR

mmmm

: register

indirect

JMP

@Rm

PC-relative

using

Rm

BRAF

Rm