Renesas SH7641 User Manual

Page 123

Section 2 CPU

Rev. 4.00 Sep. 14, 2005 Page 73 of 982

REJ09B0023-0400

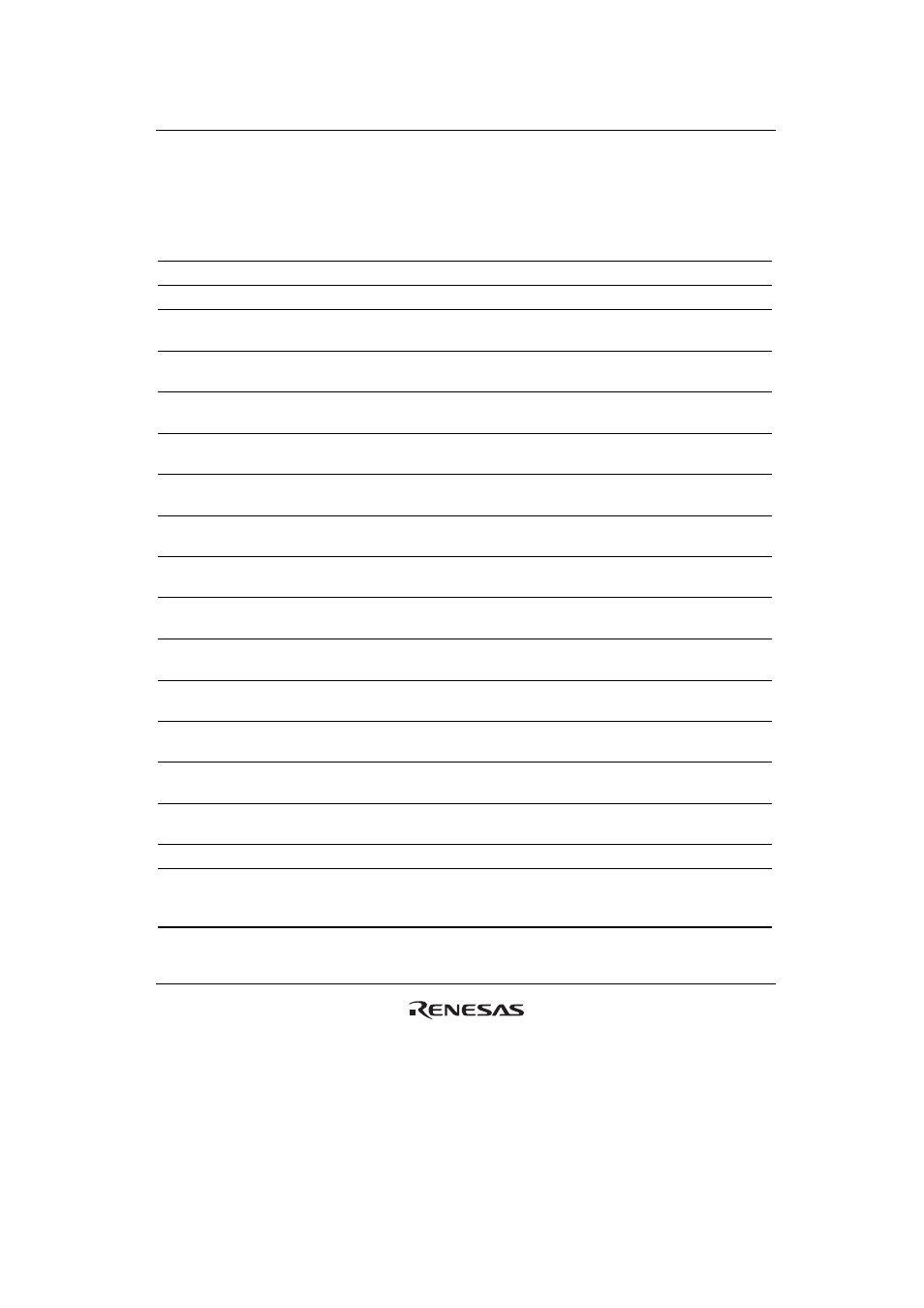

Arithmetic Operation Instructions

Table 2.20 Arithmetic Operation Instructions

Instruction

Instruction Code

Operation

Execution

States

T Bit

ADD Rm,Rn

0011nnnnmmmm1100

Rn + Rm

→ Rn

1

—

ADD #imm,Rn

0111nnnniiiiiiii

Rn + imm

→ Rn

1

—

ADDC Rm,Rn

0011nnnnmmmm1110

Rn + Rm + T

→ Rn,

Carry

→ T

1 Carry

ADDV Rm,Rn

0011nnnnmmmm1111

Rn + Rm

→ Rn,

Overflow

→ T

1 Overflow

CMP/EQ #imm,R0

10001000iiiiiiii

If R0

= imm, 1 → T

1

Comparison

result

CMP/EQ Rm,Rn 0011nnnnmmmm0000

If Rn

= Rm, 1 →

T 1 Comparison

result

CMP/HS Rm,Rn 0011nnnnmmmm0010

If Rn

≥ Rm with

unsigned data, 1

→ T

1 Comparison

result

CMP/GE Rm,Rn 0011nnnnmmmm0011

If Rn

≥ Rm with signed data,

1

→ T

1 Comparison

result

CMP/HI Rm,Rn 0011nnnnmmmm0110

If Rn > Rm with

unsigned data, 1

→ T

1 Comparison

result

CMP/GT Rm,Rn 0011nnnnmmmm0111

If Rn > Rm with signed data,

1

→ T

1 Comparison

result

CMP/PL Rn

0100nnnn00010101

If Rn > 0, 1

→ T

1

Comparison

result

CMP/PZ Rn

0100nnnn00010001

If Rn

≥ 0, 1 → T

1

Comparison

result

CMP/STR Rm,Rn

0010nnnnmmmm1100

If Rn and Rm have an

equivalent byte, 1

→ T

1 Comparison

result

DIV1 Rm,Rn

0011nnnnmmmm0100

Single-step division (Rn/Rm) 1

Calculation

result

DIV0S Rm,Rn 0010nnnnmmmm0111

MSB of Rn

→ Q,

MSB of Rm

→ M, M ^ Q → T

1 Calculation

result

DIV0U

0000000000011001

0

→ M/Q/T

1

0

DMULS.L Rm,Rn

0011nnnnmmmm1101

Signed operation of

Rn

× Rm → MACH,

MACL 32

× 32 → 64 bits

2(5) *

1

—