Renesas SH7641 User Manual

Page 491

Section 13 Direct Memory Access Controller (DMAC)

Rev. 4.00 Sep. 14, 2005 Page 441 of 982

REJ09B0023-0400

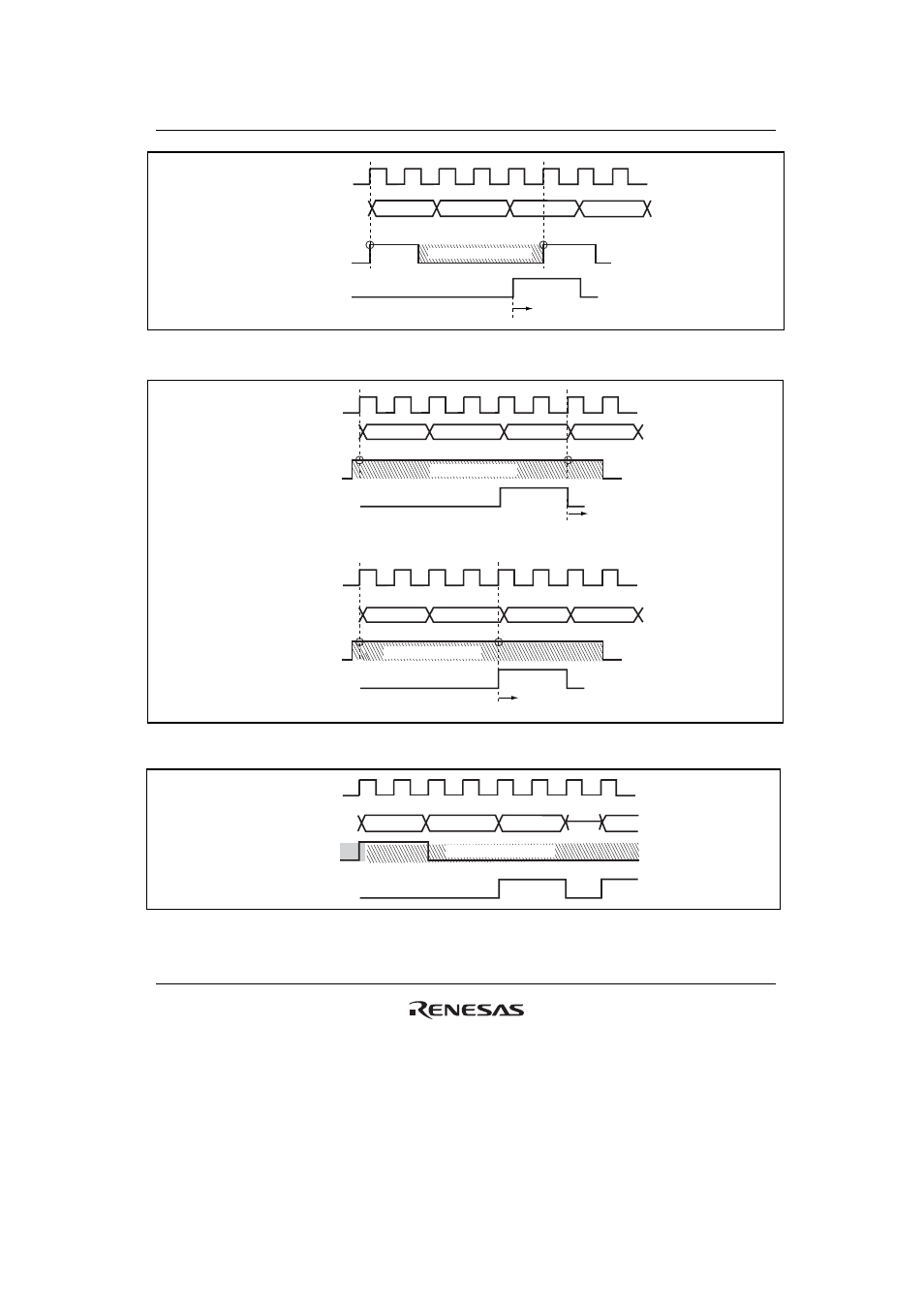

CKIO

1st acceptance

2nd acceptance

Acceptance start

Bus cycle

DREQ

(Rising)

DACK

(Active-high)

CPU

CPU

CPU

DMAC

Non sensitive period

Figure 13.13 Example of

DREQ Input Detection in Cycle Steal Mode Edge Detection

CKIO

Bus cycle

Bus cycle

DREQ

(Rising)

DACK

(Active-high)

DREQ

(Overrun 1 at

high level)

DACK

(Active-high)

CPU

CPU

CPU

DMAC

CKIO

CPU

CPU

CPU

DMAC

1st acceptance

2nd acceptance

1st acceptance

2nd acceptance

Acceptance

start

Acceptance

start

Non sensitive period

Non sensitive period

Figure 13.14 Example of

DREQ Input Detection in Cycle Steal Mode Level Detection

CKIO

DREQ

DACK

CPU

CPU

DMAC

DMAC

Bus cycle

Non sensitive period

Burst acceptance

Figure 13.15 Example of

DREQ Input Detection in Burst Mode Edge Detection