2 reset configuration, 3 tdo output timing – Renesas SH7641 User Manual

Page 519

Section 15 User Debugging Interface (H-UDI)

Rev. 4.00 Sep. 14, 2005 Page 469 of 982

REJ09B0023-0400

15.4.2 Reset

Configuration

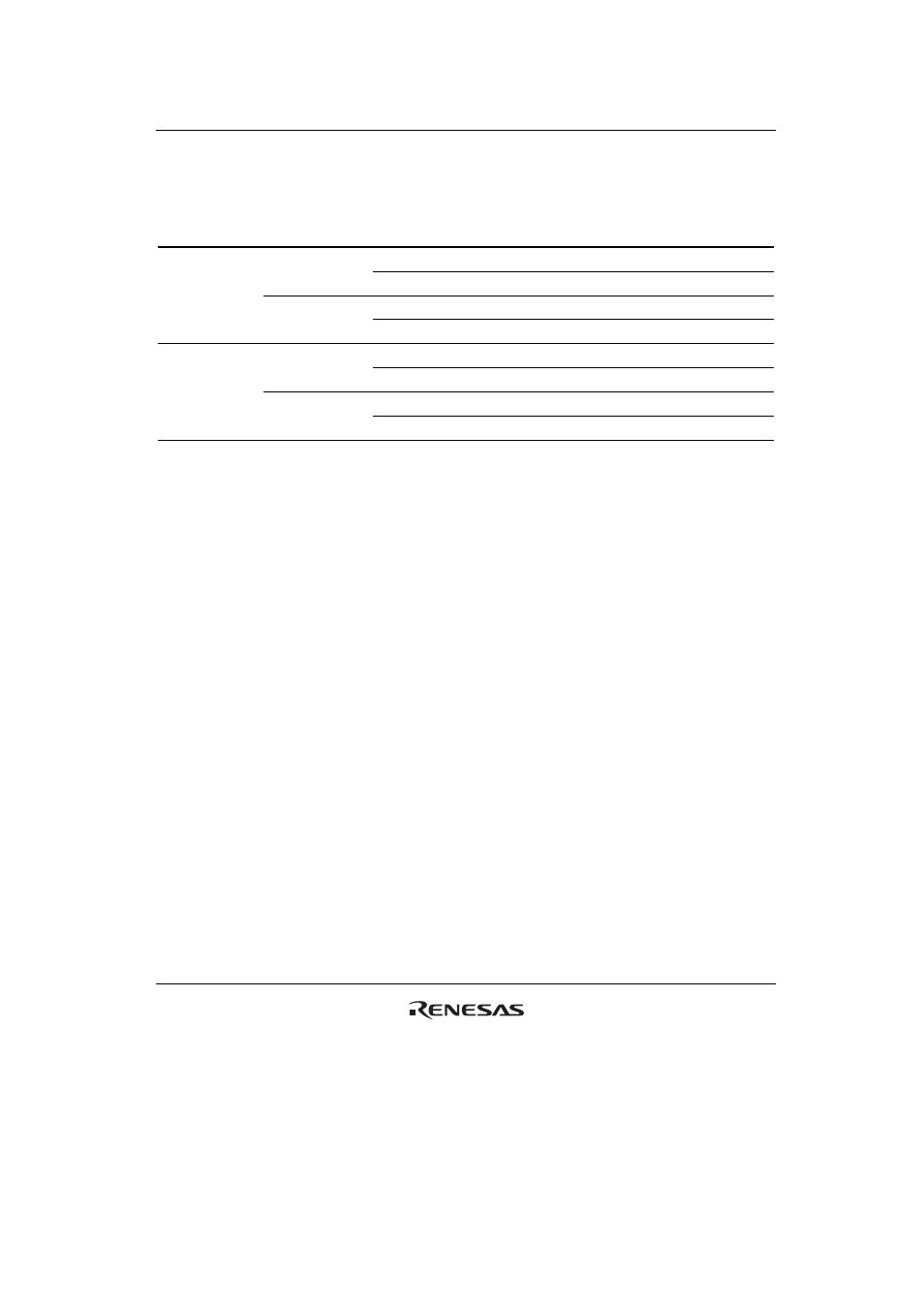

Table 15.4 Reset Configuration

ASEMD0*

1

RESETP

TRST

Chip

State

H

L

L

Normal reset and H-UDI reset

H

Normal

reset

H

L

H-UDI reset only

H

Normal

operation

L L L Reset

hold*

2

H

Normal

reset

H

L

H-UDI reset only

H

Normal

operation

Notes: 1. Performs normal mode and ASE mode settings

ASEMD0 = H, normal mode

ASEMD0 = L, ASE mode

2. In ASE mode, reset hold is entered if the

TRST pin is driven low while the RESETP pin

is negated. In this state, the CPU does not start up. When

TRST is driven high, H-UDI

operation is enabled, but the CPU does not start up. The reset hold state is cancelled

by the following:

Another

RESETP assert (power-on reset)

15.4.3

TDO Output Timing

The timing of data output from the TDO is switched by the command type set in the SDIR. The

timing changes at the TCK falling edge when JTAG commands (EXTEST, CLAMP, HIGHZ,

SAMPLE/PRELOAD, IDCODE, and BYPASS) are set. This is a timing of the JTAG standard.

When the H-UDI commands (H-UDI reset negate, H-UDI reset assert, and H-UDI interrupt) are

set, TDO is output at the TCK rising edge earlier than the JTAG standard by a half cycle.