Renesas SH7641 User Manual

Page 113

Section 2 CPU

Rev. 4.00 Sep. 14, 2005 Page 63 of 982

REJ09B0023-0400

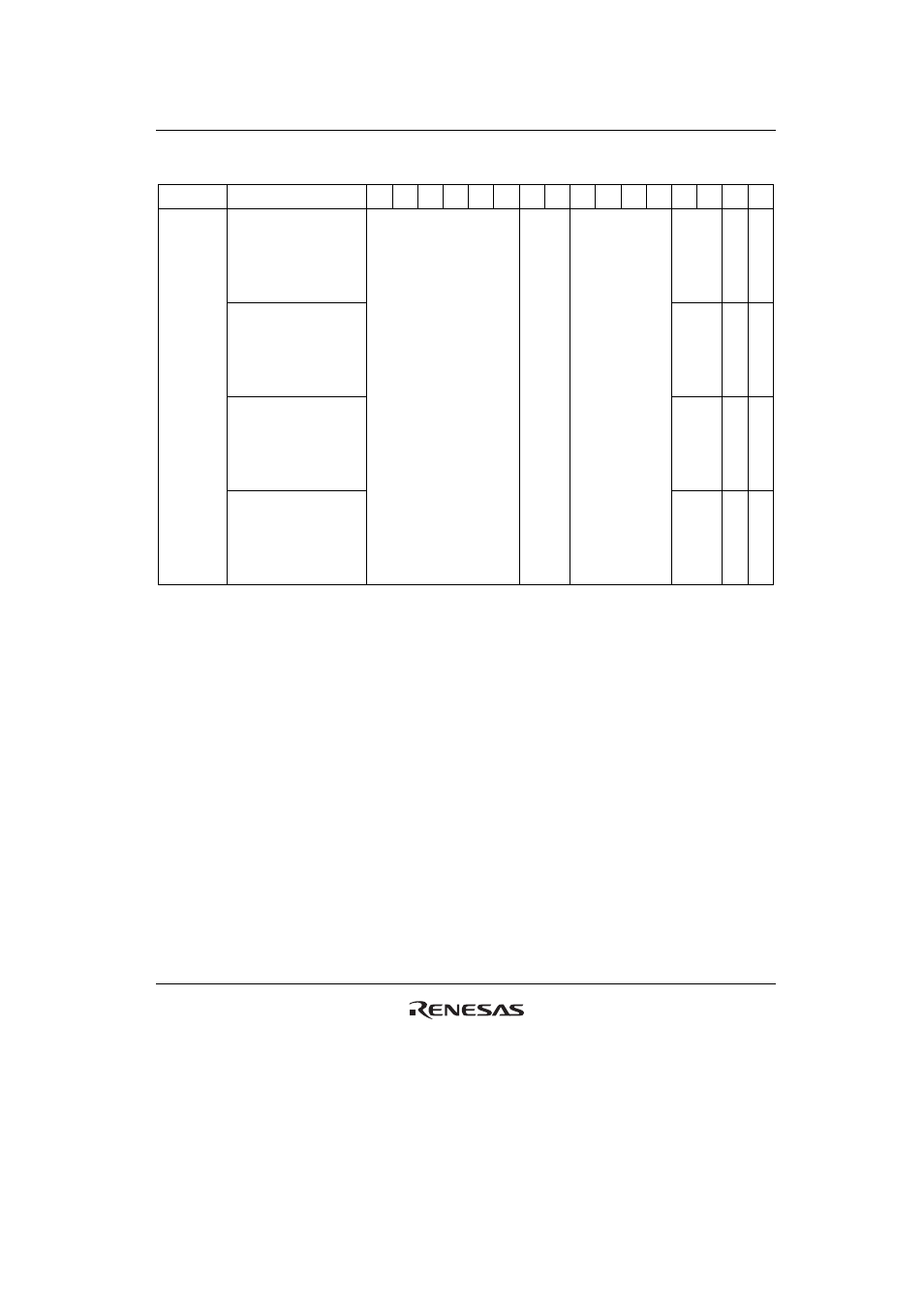

Table 2.15 Single Data Transfer Instruction Formats

Type

Mnemonic

15 14 13 12 11 10

9 8 7 6 5 4 3 2 1 0

Single

MOVS.W

@-As,Ds 1 1 1 1 0 1 As

Ds

0:(*)

0 0 0 0

data

MOVS.W

@As,Ds 0:R4 1:(*) 0

1

transfer MOVS.W

@As+,Ds 1:R5 2:(*) 1

0

MOVS.W

@As+Ix,Ds

2:R2 3:(*) 1

1

MOVS.W

Ds,@-As 3:R3 4:(*)

0 0 0 1

MOVS.W

Ds,@As

5:A1 0

1

MOVS.W

Ds,@As+

6:(*) 1

0

MOVS.W

Ds,@As+Ix

7:A0 1

1

MOVS.L

@-As,Ds

8:X0 0

0

1

0

MOVS.L

@As,Ds

9:X1 0

1

MOVS.L

@As+,Ds

A:Y0 1

0

MOVS.L

@As+Ix,Ds

B:Y1 1

1

MOVS.L

Ds,@-As

C:M0 0

0

1

1

MOVS.L

Ds,@As

D:A1G

0

1

MOVS.L

Ds,@As+

E:M1 1

0

MOVS.L

Ds,@As+Ix

F:A0G 1

1

Note: * Codes reserved for system use.

Parallel Processing Instructions: Parallel processing instructions are provided for efficient

execution of digital signal processing using the DSP unit. They are 32 bits long and allow four

simultaneous processes, an ALU operation, multiplication, and two data transfers.

Parallel processing instructions are divided into an A field and a B field. The A field defines data

transfer instructions and the B field an ALU operation instruction and multiply instruction. These

instructions can be defined independently, and the processing is executed in parallel,

independently and simultaneously. A-field parallel data transfer instructions are shown in table

2.16, and B-field ALU operation instructions and multiply instructions in table 2.17.