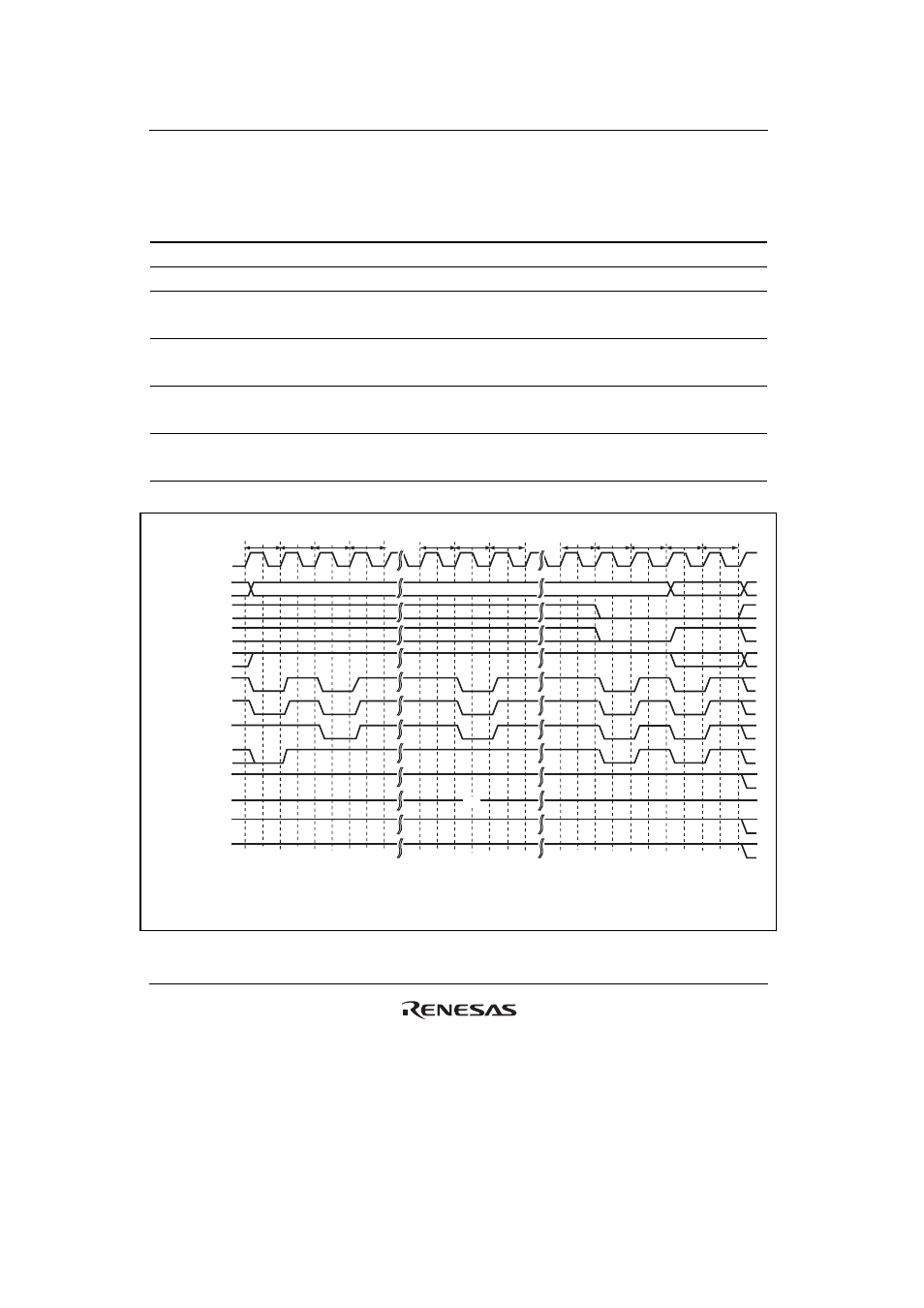

Figure 12.34 emrs command issue timing – Renesas SH7641 User Manual

Page 424

Section 12 Bus State Controller (BSC)

Rev. 4.00 Sep. 14, 2005 Page 374 of 982

REJ09B0023-0400

Table 12.16 Output Addresses when EMRS Command Is Issued

Command to be

Issued

Access

Address

Access Data

Write

Access

Size

MRS

Command

Issue Address

EMRS

Command

Issue Address

CS2 MRS

H'A4FD4XX0 H'******** 16

bits H'0000XX0

CS3 MRS

H'A4FD5XX0 H'******** 16

bits H'0000XX0

CS2 MRS + EMRS

(with refresh)

H'A4FD4XX0 H'0YYYYYYY 32

bits H'0000XX0

H'YYYYYYY

CS3 MRS + EMRS

(with refresh)

H'A4FD5XX0 H'0YYYYYYY 32

bits H'0000XX0

H'YYYYYYY

CS2 MRS + EMRS

(without refresh)

H'A4FD4XX0 H'1YYYYYYY 32

bits H'0000XX0

H'YYYYYYY

CS3 MRS + EMRS

(without refresh)

H'A4FD5XX0 H'1YYYYYYY 32

bits H'0000XX0

H'YYYYYYY

CKIO

A25 to A0

CSn

RD/

WR

RASL, RASU

DQMxx

D31 to D0

BS

Tpw

DACKn*

4

Tp

Trr

A12/A11*

3

BA1*

1

BA0*

2

CASL, CASU

Notes: 1. Address pin to be connected to pin BA1 of SDRAM.

2. Address pin to be connected to pin BA0 of SDRAM.

3. Address pin to be connected to pin A10 of SDRAM.

4. The waveform for

DACKn is when active low is specified.

Trc

Trc

Tmw

Hi-Z

Tnop

Trc

Trr

Trc

REF

REF

MRS

Temw Tnop

EMRS

PALL

Figure 12.34 EMRS Command Issue Timing