3 ac bus timing – Renesas SH7641 User Manual

Page 973

Section 25 Electrical Characteristics

Rev. 4.00 Sep. 14, 2005 Page 923 of 982

REJ09B0023-0400

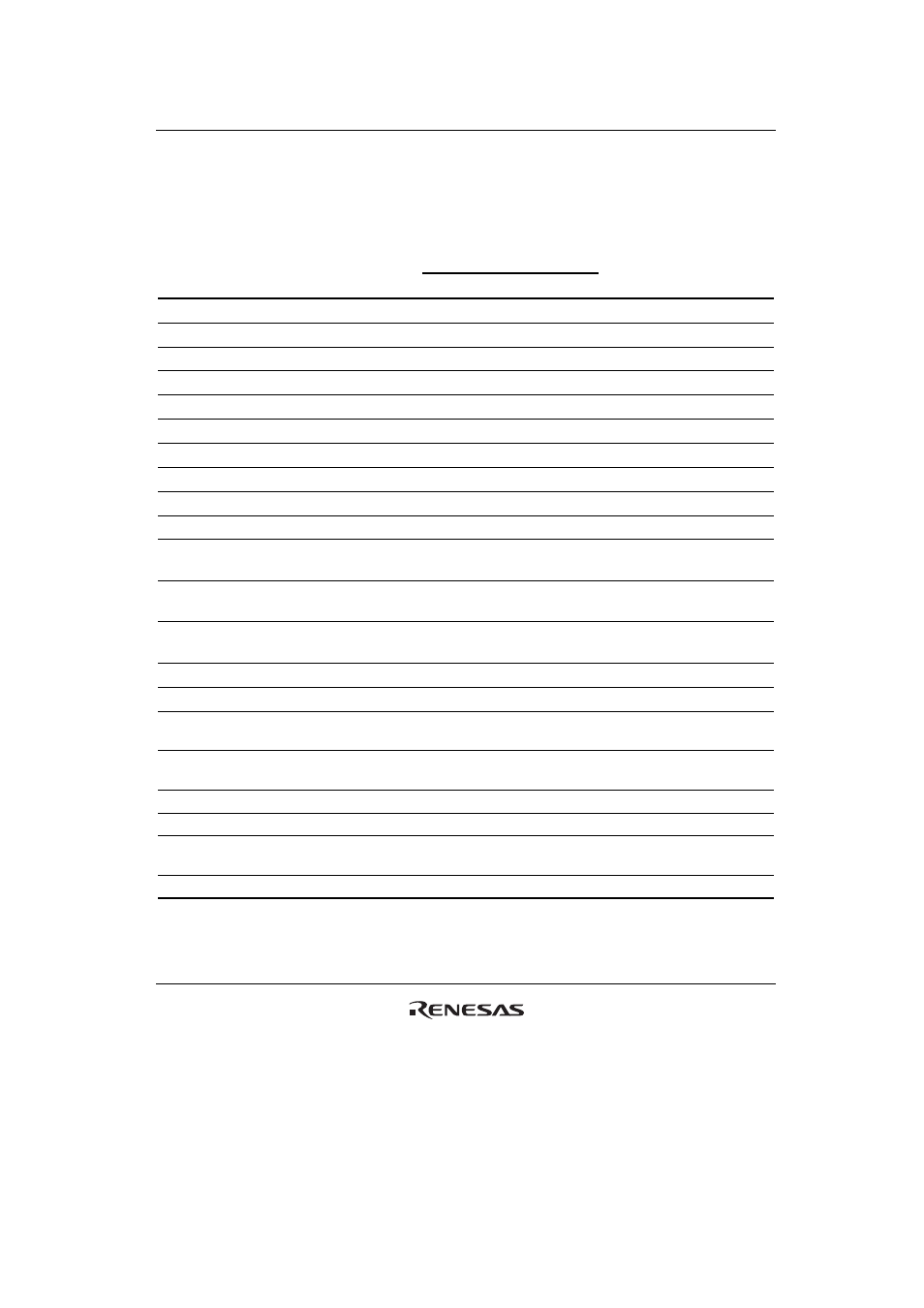

25.3.3

AC Bus Timing

Table 25.8 Bus Timing

Conditions: Clock mode 2/6/7, V

CC

Q

= 3.0 V to 3.6 V, V

SS

Q = 0 V, Ta

= −40°C to +85°C

B

φ

= 50 MHz

*

Item Symbol

Min.

Max.

Unit

Figure(s)

Address delay time 1

t

AD1

1

12

ns

25.13 to 25.39

Address delay time 2

t

AD2

1/2t

cyc

1/2t

cyc

+ 12

ns

25.22

Address delay time 3

t

AD3

1/2t

cyc

1/2t

cyc

+ 12

ns

25.40, 25.41

Address setup time

t

AS

0

—

ns

25.13 to 25.18

Address hold time

t

AH

0

—

ns

25.13 to 25.17

BS delay time

t

BSD

—

12

ns

25.13 to 25.36

CS delay time 1

t

CSD1

1

12

ns

25.13 to 25.39

CS delay time 2

t

CSD2

1/2t

cyc

1/2t

cyc

+ 12

ns

25.40, 25.41

Read write delay time 1

t

RWD1

1

12

ns

25.13 to 25.39

Read write delay time 2

t

RWD2

1/2t

cyc

1/2t

cyc

+ 12

ns

25.40, 25.41

Read strobe delay time

t

RSD

1/2t

cyc

1/2t

cyc

+ 12

ns

25.13 to 25.18,

25.20 to 25.22

Read data setup time 1

t

RDS1

1/2t

cyc

+ 8

—

ns

25.13 to 25.18,

25.20, 25.21

Read data setup time 2

t

RDS2

8

—

ns

25.23 to 25.26,

25.31 to 25.33

Read data setup time 3

t

RDS3

1/2t

cyc

+ 8

—

ns

25.22

Read data setup time 4

t

RDS4

1/2t

cyc

+ 8

—

ns

25.40

Read data hold time 1

t

RDH1

0

—

ns

25.13 to 25.18,

25.20

Read data hold time 2

t

RDH2

2

—

ns

25.23 to 25.26,

25.31 to 25.33

Read data hold time 3

t

RDH3

0

—

ns 25.22

Read data hold time 4

t

RDH4

1/2t

cyc

+ 5

—

ns

25.40

Write enable delay time 1

t

WED1

1/2t

cyc

1/2t

cyc

+ 12

ns

25.13 to 25.18,

25.20

Write enable delay time 2

t

WED2

—

12

ns 25.21