9 burst mpx-i/o interface – Renesas SH7641 User Manual

Page 432

Section 12 Bus State Controller (BSC)

Rev. 4.00 Sep. 14, 2005 Page 382 of 982

REJ09B0023-0400

12.5.9 Burst

MPX-I/O

Interface

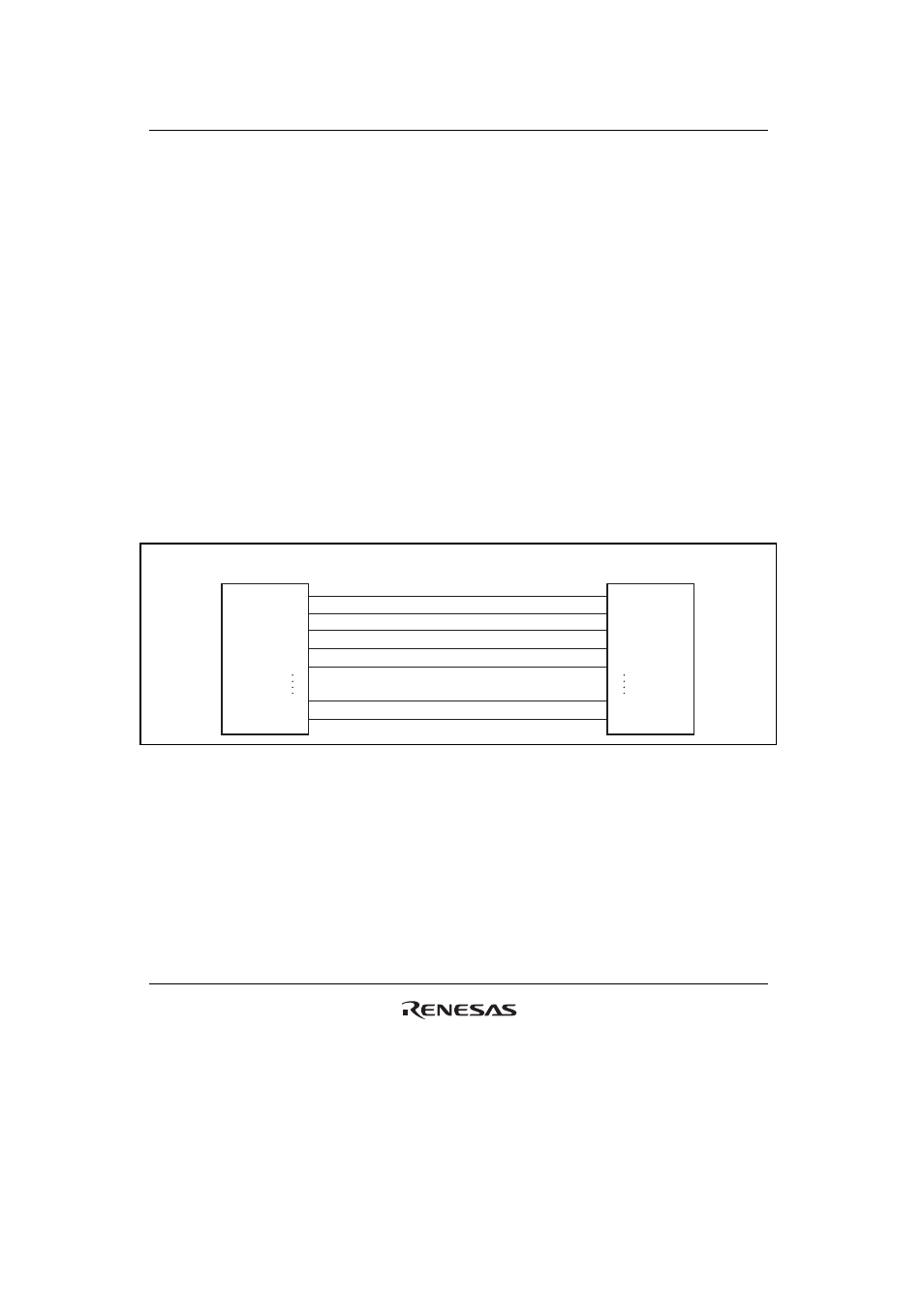

Figure 12.42 shows an example of a connection between the LSI and an MPX device. Figures

12.43 to 12.46 show the burst MPX space access timings.

Area 6 can be specified as the address/data multiplex I/O (MPX-I/O) interface using the TYPE2 to

TYPE0 bits in the CS6BCR register. This MPX-I/O interface enables the LSI to be easily

connected to an external memory controller chip that uses an address/data multiplexed 32-bit

single bus. In this case, the address and the access size for the MPX-I/O interface are output to

D25 to D0 and D31 to D29, respectively, in address cycles. For the access sizes of D31 to D29,

see the description of the CS6BWCR register (burst MPX-I/O). Address pins A25 to A0 are used

to output normal addresses.

In the burst MPX-I/O interface, the bus size is fixed at 32 bits. The BSZ1 and BSZ0 bits in

CS6BBCR must be specified as 32 bits.

In the MPX-I/O interface, a software wait or hardware wait can be inserted using the

WAIT pin.

In read cycles, a wait cycle is inserted automatically following the address output even if the

software wait insertion is specified as 0.

This LSI

CS

BS

FRAME

WE

I/O31

I/O0

WAIT

CS6B

BS

FRAME

RD/

WR

D31

D0

WAIT

64k

× 16-bit

SRAM

Figure 12.42 Burst MPX Device Connection Example