Renesas SH7641 User Manual

Page 124

Section 2 CPU

Rev. 4.00 Sep. 14, 2005 Page 74 of 982

REJ09B0023-0400

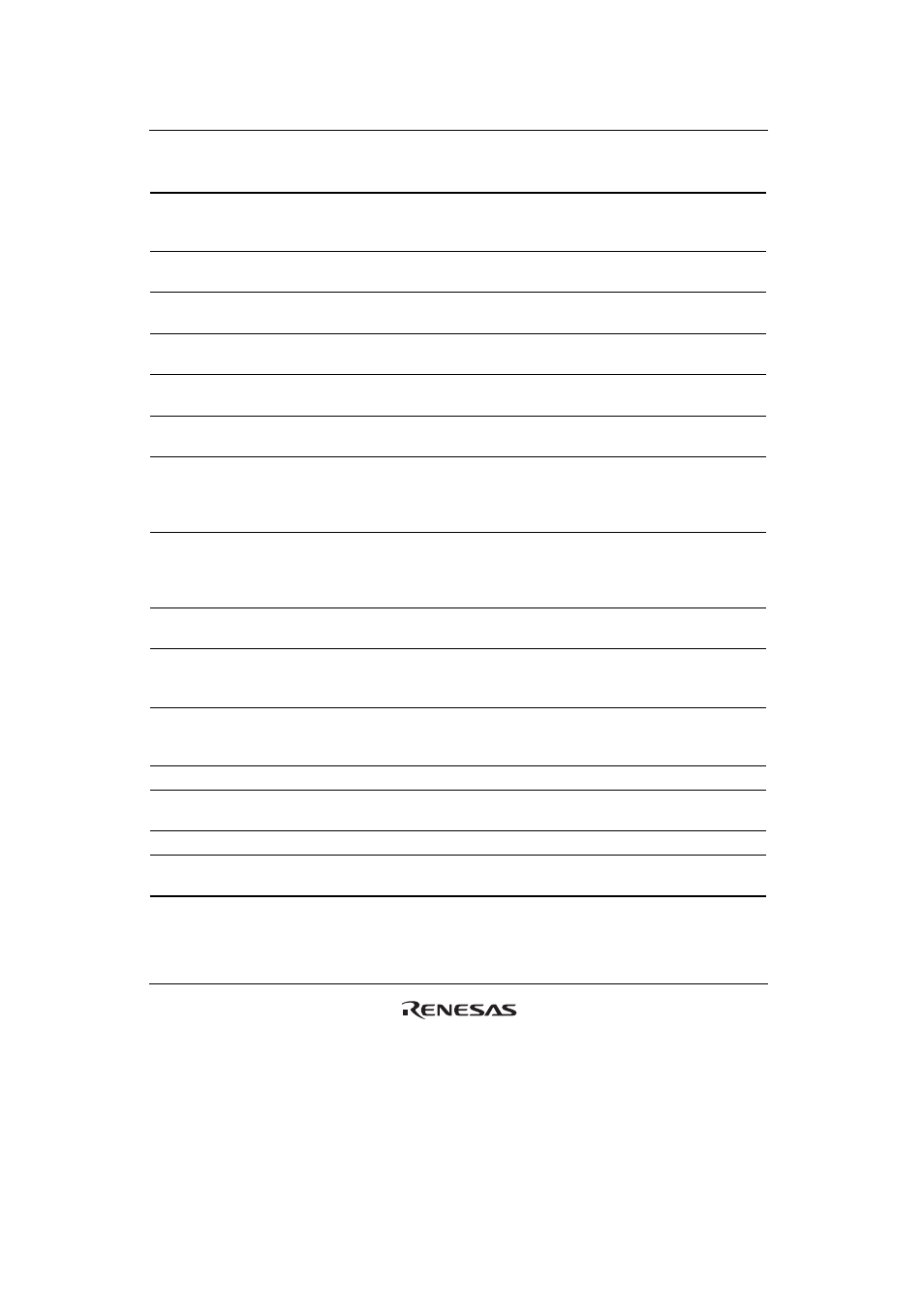

Instruction

Instruction Code

Operation

Execution

States

T Bit

DMULU.L Rm,Rn

0011nnnnmmmm0101

Unsigned operation of

Rn

× Rm → MACH,

MACL 32

× 32 → 4 bits

2(5) *

1

—

DT Rn

0100nnnn00010000

Rn – 1

→ Rn, if Rn = 0, 1

→ T, else 0 → T

1 Comparison

result

EXTS.B Rm,Rn

0110nnnnmmmm1110

A byte in Rm is sign-extended

→ Rn

1 —

EXTS.W Rm,Rn

0110nnnnmmmm1111

A word in Rm is sign-extended

→ Rn

1 —

EXTU.B Rm,Rn

0110nnnnmmmm1100

A byte in Rm is zero-extended

→ Rn

1 —

EXTU.W Rm,Rn

0110nnnnmmmm1101

A word in Rm is zero-extended

→ Rn

1 —

MAC.L @Rm+,@Rn+ 0000nnnnmmmm1111

Signed operation of (Rn)

× (Rm) → MAC → MAC,

Rn + 4

→ Rn, Rm + 4 → Rm

32

× 32 + 64 → 64 bits

2(5)*

1

—

MAC.W @Rm+,@Rn+ 0100nnnnmmmm1111

Signed operation of (Rn)

× (Rm) → MAC → MAC,

Rn + 2

→ Rn, Rm + 2 → Rm

16

× 16 + 64 → 64 bits

2(5)*

1

—

MUL.L Rm,Rn

0000nnnnmmmm0111

Rn

× Rm → MACL

32

× 32 → 32 bits

2(5)*

1

—

MULS.W Rm,Rn

0010nnnnmmmm1111

Signed operation of

Rn

× Rm → MAC

16

× 16 → 32 bits

1(3)*

2

—

MULU.W Rm,Rn

0010nnnnmmmm1110

Unsigned operation of

Rn

× Rm → MAC

16

× 16 → 32 bits

1(3)*

2

—

NEG Rm,Rn

0110nnnnmmmm1011

0–Rm

→ Rn

1

—

NEGC Rm,Rn

0110nnnnmmmm1010

0–Rm–T

→ Rn,

Borrow

→ T

1 Borrow

SUB Rm,Rn

0011nnnnmmmm1000

Rn–Rm

→ Rn

1

—

SUBC Rm,Rn

0011nnnnmmmm1010

Rn–Rm–T

→ Rn,

Borrow

→ T

1 Borrow