2 block diagram, Figure 1.1 block diagram – Renesas SH7641 User Manual

Page 57

Section 1 Overview

Rev. 4.00 Sep. 14, 2005 Page 7 of 982

REJ09B0023-0400

1.2 Block

Diagram

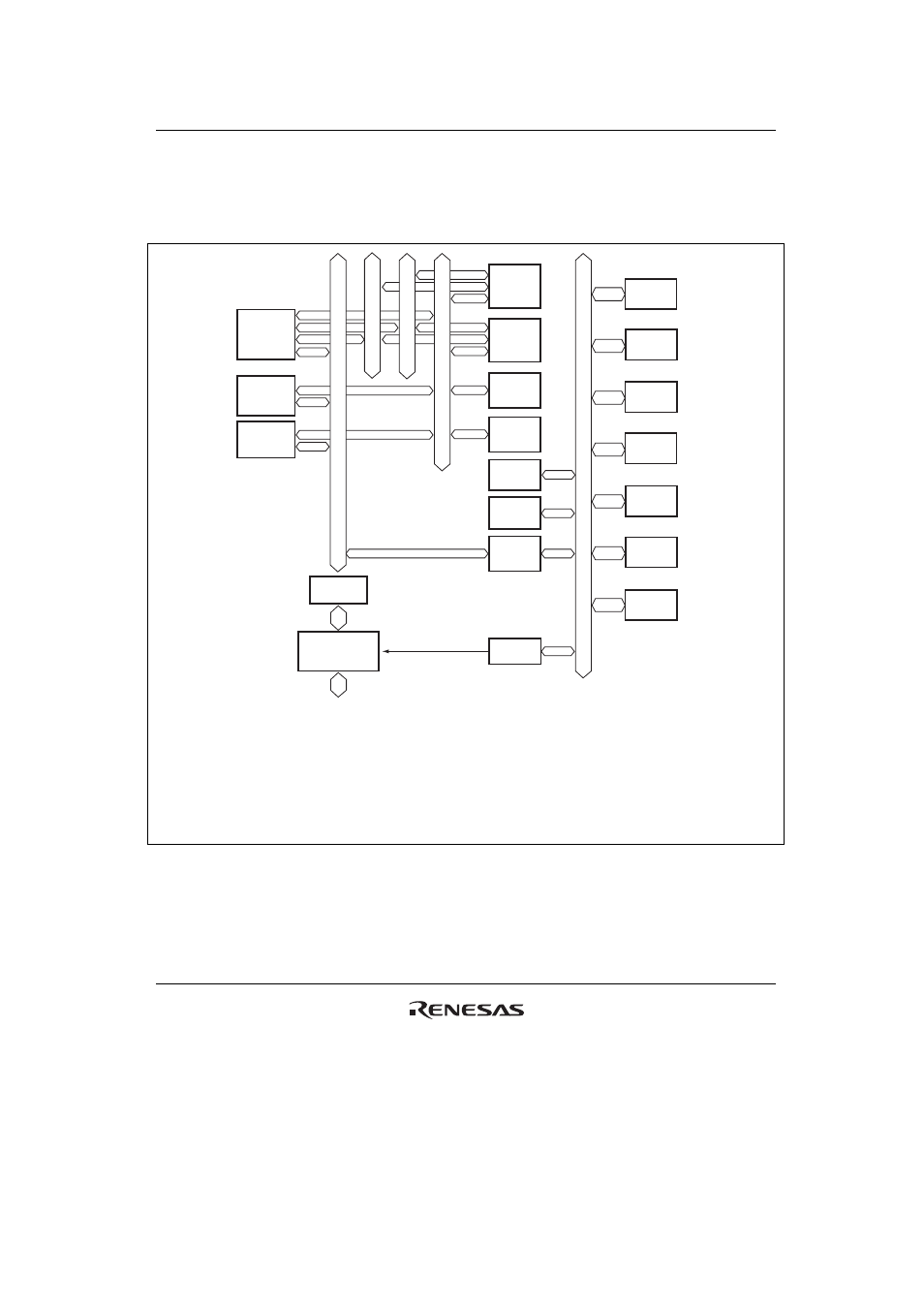

The block diagram of this LSI is shown in figure1.1.

X/Y

Memory

SH3

CPU

MTU

CMT

SCIF

IIC2

H-UDI

USB

DSP

UBC

AUD

ADC

BSC

DMAC

U Memory

CACHE

INTC

CPG/

WDT

External Bus

Interface

Y-BUS

I-BUS

X-BUS

L-BUS

Peripheral-BUS

I/O port

[Legend]

ADC:

AUD:

BSC:

CACHE:

CMT:

CPG/WDT:

CPU:

DMAC:

A/D converter

Advanced user debugger

Bus state controller

Cache memory

Compare match timer

Clock Pulse generator/Watch dog Timer

Central processing unit

Direct memory access controller

DSP:

H-UDI:

INTC:

SCIF:

UBC:

MTU:

USB :

IIC2:

Digital signal processor

User debugging interface

Interrupt controller

Serial communication interface

User break controller

Multi-Function Timer Pulse unit

USB function module

I

2

C bus interface

Figure 1.1 Block Diagram