3 port pin data/set data registers (portnp/setn) – Motorola ColdFire MCF5281 User Manual

Page 513

General Purpose I/O Module

Freescale Semiconductor

26-13

26.3.2.3

Port Pin Data/Set Data Registers (PORTnP/SETn)

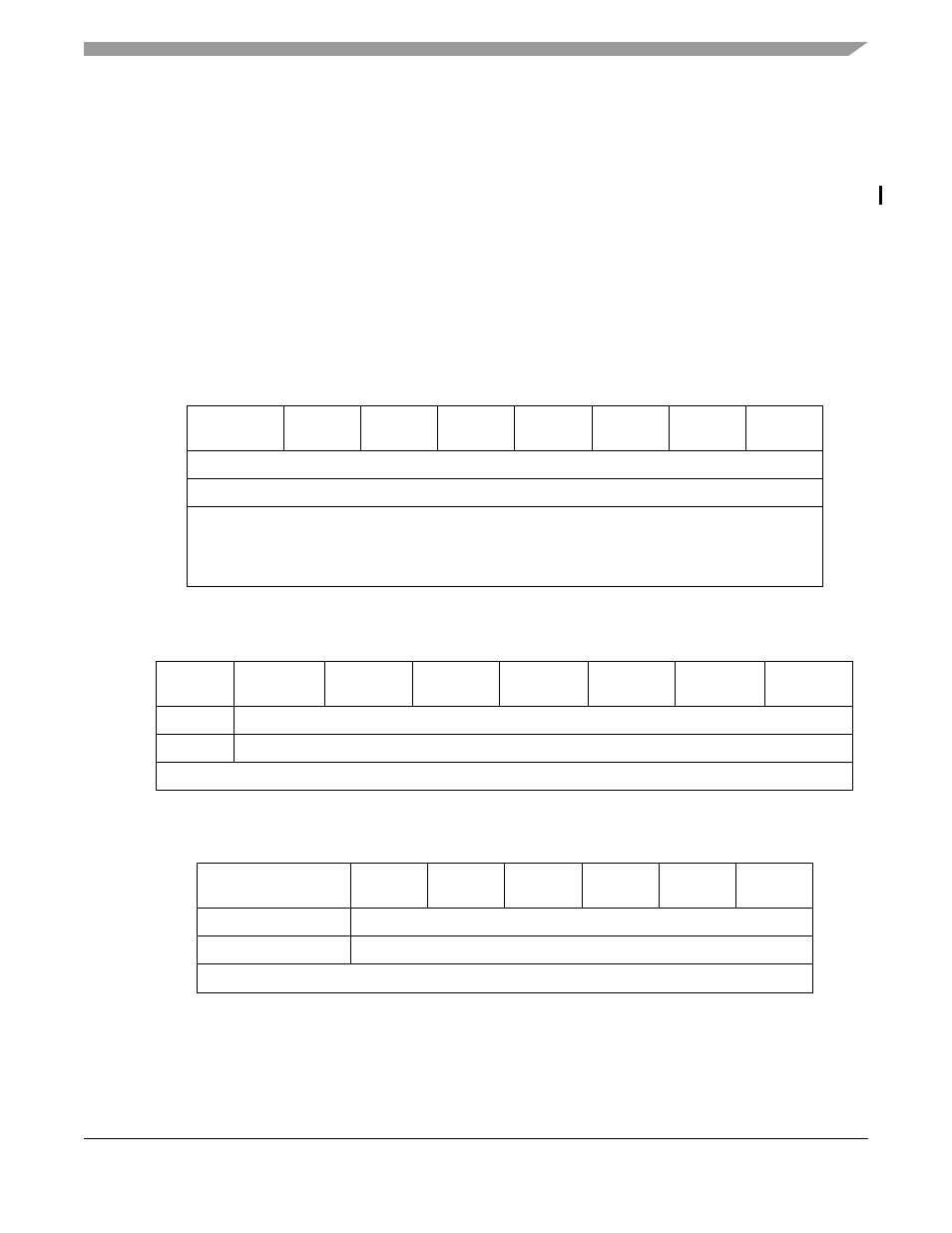

The PORTnP/SETn registers reflect the current pin states and control the setting of output pins when the

pin is configured for digital I/O.

Most PORTn registers have a full 8-bit implementation, as shown in

. The remaining PORTn

registers use fewer than eight bits. Their bit definitions are shown in

, and

.

The PORTnP/SETn registers are read/write. At reset, the bits in the PORTnP/SETn registers are set to the

current pin states.

Reading a PORTnP/SETn register returns the current state of the port n pins.

Setting a PORTnP/SETn register sets the corresponding bits in the PORTn register. Writing 0s has no

effect.

7

6

5

4

3

2

1

0

Field

PORTnP7/

SETn7

PORTnP6/

SETn6

PORTnP5/

SETn5

PORTnP4/

SETn4

PORTnP3/

SETn3

PORTnP2/

SETn2

PORTnP1/

SETn1

PORTnP0/

SETn0

Reset

Current Pin State

R/W:

R/W

Address IPSBAR + 0x10_0028 (PORTAP/SETA), 0x10_0029 (PORTBP/SETB), 0x10_002A (PORTCP/SETC),

0x10_002B (PORTDP/SETD), 0x10_002C (PORTEP/SETE), 0x10_002D (PORTFP/SETF),

0x10_002E (PORTGP/SETG), 0x10_002F (PORTHP/SETH), 0x10_0030 (PORTJP/SETJ), 0x10_0031

(PORTDDP/SETDD), 0x10_0032 (PORTEHP/SETEH), 0x10_0033 (PORTELP/SETEL)

Figure 26-11. Port Pin Data/Set Data Registers (8-bit)

7

6

5

4

3

2

1

0

Field

—

PORTnP6/S

ETn6

PORTnP5/S

ETn5

PORTnP4/S

ETn4

PORTnP3/S

ETn3

PORTnP2/S

ETn2

PORTnP1/S

ETn1

PORTnP0/S

ETn0

Reset

0

Current Pin State

R/W:

—

R/W

Address

IPSBAR + 0x10_0035 (PORTQSP/SETQS)

Figure 26-12. Port Pin Data/Set Data Register (7-bit)

7

6

5

4

3

2

1

0

Field

—

PORTnP5/

SETn5

PORTnP4/

SETn4

PORTnP3/

SETn3

PORTnP2/

SETn2

PORTnP1/

SETn1

PORTnP0/

SETn0

Reset

00

Current Pin State

R/W:

—

R/W

Address

IPSBAR + 0x10_0034 (PORTASP/SETAS), 0x10_0036 (PORTSDP/SETSD)

Figure 26-13. Port Pin Data/Set Data Registers (6-bit)

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3