7 branch instruction execution times, 7 branch instruction execution times -32 – Motorola ColdFire MCF5281 User Manual

Page 78

ColdFire Core

2-32

Freescale Semiconductor

NOTE

The execution times for moving the contents of the Racc, Raccext[01,23],

MACSR, or Rmask into a destination location

represent the best-case scenario when the store instruction is executed and

there are no load or M{S}AC instructions in the EMAC execution pipeline.

In general, these store operations require only a single cycle for execution,

but if preceded immediately by a load, MAC, or MSAC instruction, the

depth of the EMAC pipeline is exposed and the execution time is four

cycles.

2.3.5.7

Branch Instruction Execution Times

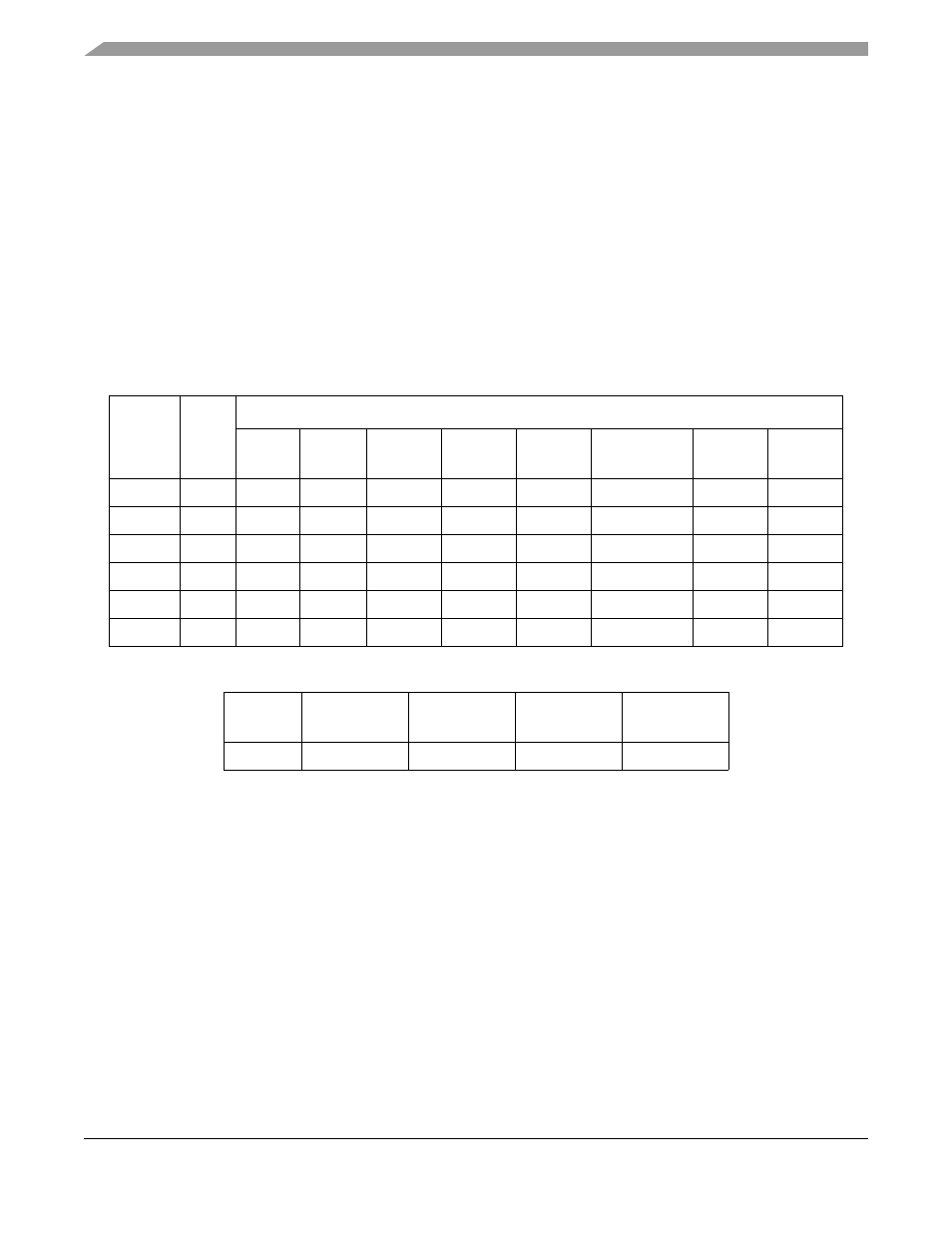

Table 2-18. General Branch Instruction Execution Times

Opcode

Effective Address

Rn

(An)

(An)+

-(An)

(d16,An)

(d16,PC)

(d8,An,Xi*SF)

(d8,PC,Xi*SF)

xxx.wl

#xxx

BRA

—

—

—

—

2(0/1)

—

—

—

BSR

—

—

—

—

3(0/1)

—

—

—

JMP

—

3(0/0)

—

—

3(0/0)

4(0/0)

3(0/0)

—

JSR

—

3(0/1)

—

—

3(0/1)

4(0/1)

3(0/1)

—

RTE

—

—

10(2/0)

—

—

—

—

—

RTS

—

—

5(1/0)

—

—

—

—

—

Table 2-19. Bcc Instruction Execution Times

Opcode

Forward

Taken

Forward

Not Taken

Backward

Taken

Backward

Not Taken

Bcc

3(0/0)

1(0/0)

2(0/0)

3(0/0)

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3