11 loss of clock in stop mode, 11 loss of clock in stop mode -16 – Motorola ColdFire MCF5281 User Manual

Page 186

Clock Module

9-16

Freescale Semiconductor

A special loss-of-clock condition occurs when both the reference and the PLL fail. The failures may be

simultaneous, or the PLL may fail first. In either case, the reference clock failure takes priority and the

PLL attempts to operate in SCM. If successful, the PLL remains in SCM until the next reset. If the PLL

cannot operate in SCM, the system remains static until the next reset. Both the reference and the PLL must

be functioning properly to exit reset.

9.7.4.11

Loss of Clock in Stop Mode

shows the resulting actions for a loss of clock in Stop Mode when the device is being clocked

by the various clocking methods.

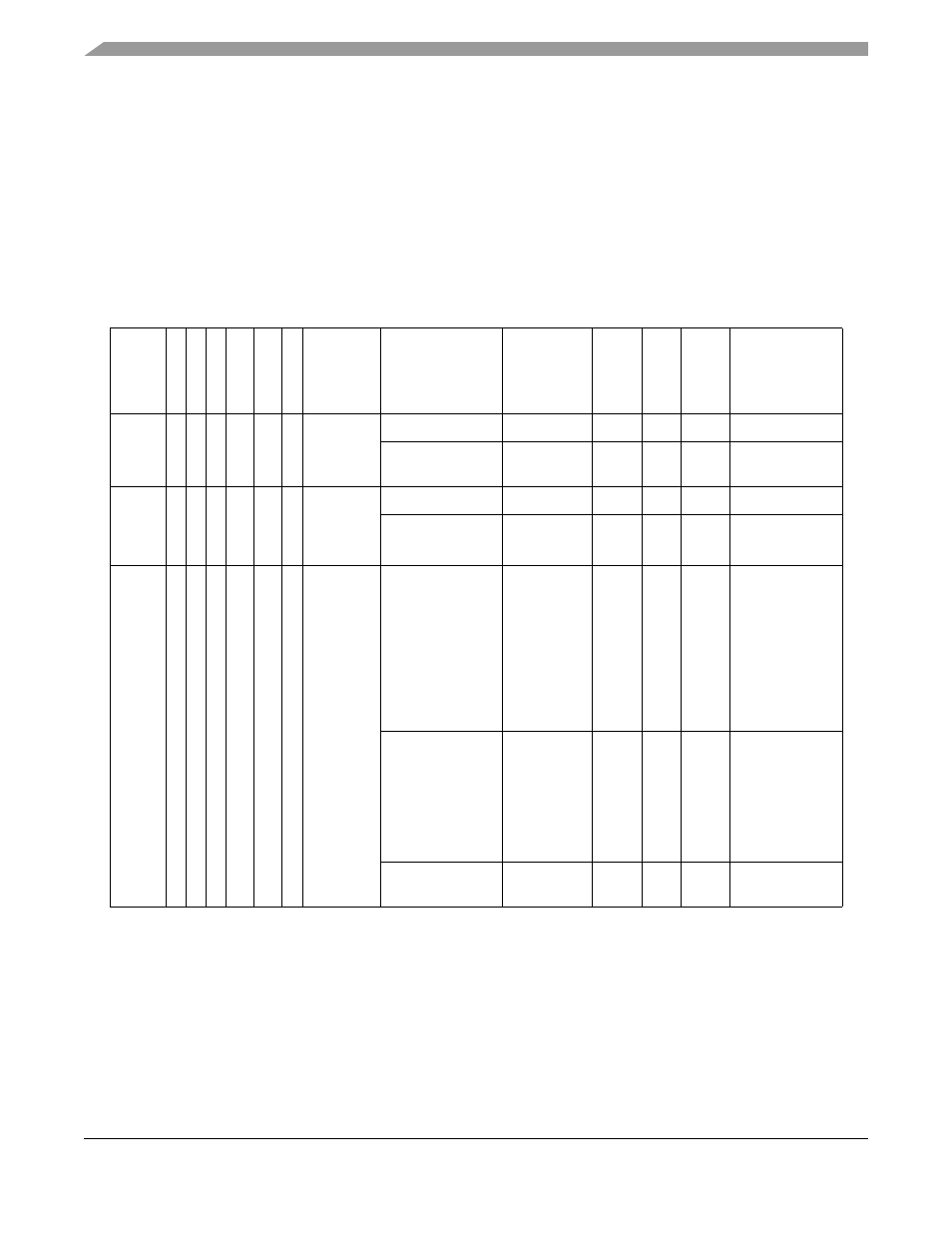

Table 9-10. Stop Mode Operation (Sheet 1 of 5)

MODE

In

LO

CEN

LOCRE

LO

L

R

E

PLL

OSC

FWKUP

Expected

PLL

Action at

Stop

PLL Action

During Stop

MODE

Out

LOCKSS

LO

CK

LO

CS

Comments

EXT

X X X X

X

X

—

—

EXT

0

0

0

Lose reference

clock

Stuck

—

—

—

NRM

0 0 0 Off Off 0 Lose lock,

f.b. clock,

reference

clock

Regain

NRM

‘LK

1

‘LC

No regain

Stuck

—

—

—

NRM

X 0 0 Off Off 1 Lose lock,

f.b. clock,

reference

clock

Regain clocks, but

don’t regain lock

SCM–>

unstable

NRM

0–>‘L

K

0–>

1

1–>‘L

C

Block LOCS and

LOCKS until

clock and lock

respectively

regain; enter

SCM regardless

of LOCEN bit

until reference

regained

No reference

clock regain

SCM–>

0–>

0–>

1–>

Block LOCS and

LOCKS until

clock and lock

respectively

regain; enter

SCM regardless

of LOCEN bit

No f.b. clock

regain

Stuck

—

—

—

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3