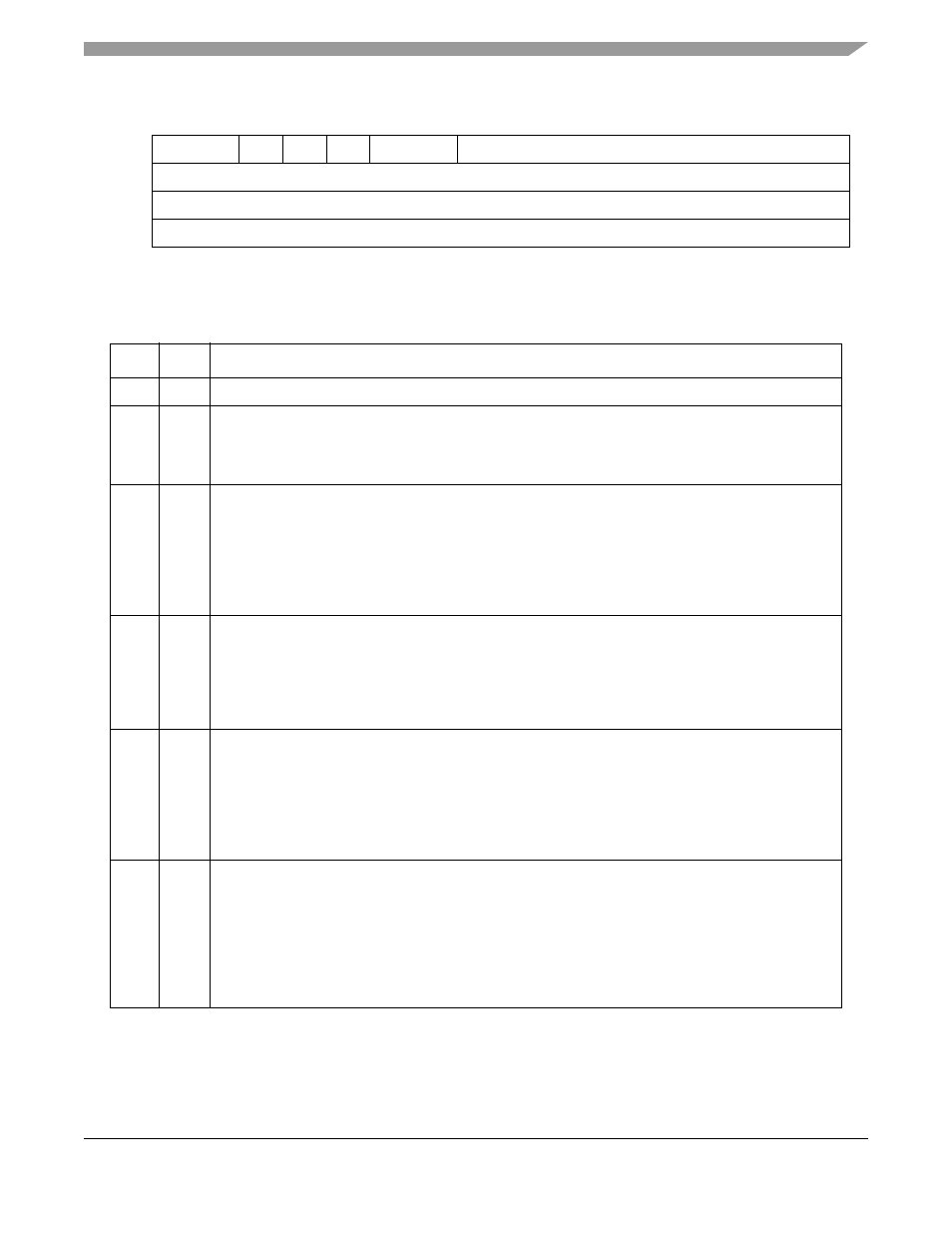

The dcr, shown in, Figure 15-2, Table 15-4 describes dcr fields – Motorola ColdFire MCF5281 User Manual

Page 277

Synchronous DRAM Controller Module

Freescale Semiconductor

15-5

describes DCR fields.

15

14

13

12

11

10

9

8

0

Field

—

NAM COC

IS

RTIM

RC

Reset

Uninitialized

R/W

R/W

Addr

IPSBAR + 0x040

Figure 15-2. DRAM Control Register (DCR)

Table 15-4. DCR Field Descriptions

Bits

Name

Description

15-14

—

Reserved, should be cleared.

13

NAM

No address multiplexing. Some implementations require external multiplexing. For example, when

linear addressing is required, the SDRAM should not multiplex addresses on SDRAM accesses.

0 The SDRAM controller multiplexes the external address bus to provide column addresses.

1 The SDRAM controller does not multiplex the external address bus to provide column addresses.

12

COC

Command on SDRAM clock enable (SCKE). Implementations that use external multiplexing (NAM = 1)

must support command information to be multiplexed onto the SDRAM address bus.

0 SCKE functions as a clock enable; self-refresh is initiated by the SDRAM controller through

DCR[IS].

1 SCKE drives command information. Because SCKE is not a clock enable, self-refresh cannot be

used (setting DCR[IS]). Thus, external logic must be used if this functionality is desired. External

multiplexing is also responsible for putting the command information on the proper address bit.

11

IS

Initiate self-refresh command.

0 Take no action or issue a

SELFX

command to exit self refresh.

1 If DCR[COC] = 0, the SDRAM controller sends a

SELF

command to both SDRAM blocks to put them

in low-power, self-refresh state where they remain until IS is cleared. When IS is cleared, the

controller sends a

SELFX

command for the SDRAMs to exit self-refresh. The refresh counter is

suspended while the SDRAMs are in self-refresh; the SDRAM controls the refresh period.

10–9

RTIM

Refresh timing. Determines the timing operation of auto-refresh in the SDRAM controller. Specifically,

it determines the number of bus clocks inserted between a

REF

command and the next possible

ACTV

command. This same timing is used for both memory blocks controlled by the SDRAM controller. This

corresponds to t

RC

in the SDRAM specifications.

00 3 clocks

01 6 clocks

1x 9 clocks

8–0

RC

Refresh count. Controls refresh frequency. The number of bus clocks between refresh cycles is

(RC + 1) x 16. Refresh can range from 16–8192 bus clocks to accommodate both standard and

low-power SDRAMs with bus clock operation from less than 2 MHz to greater than 50 MHz.

The following example calculates RC for an auto-refresh period for 4096 rows to receive 64 ms of

refresh every 15.625 µs for each row (1031 bus clocks at 66 MHz). This operation is the same as in

asynchronous mode.

# of bus clocks = 1031 = (RC field + 1) x 16

RC = (1031 bus clocks/16) -1 = 63.44, which rounds to 63; therefore, RC = 0x3F.

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3