3 memory map and register definition, 4 register descriptions, Memory map and register definition -2 – Motorola ColdFire MCF5281 User Manual

Page 154: Register descriptions -2

System Control Module (SCM)

8-2

Freescale Semiconductor

8.3

Memory Map and Register Definition

The memory map for the SCM registers is shown in

. All the registers in the SCM are

memory-mapped as offsets within the 1 Gbyte IPS address space and accesses are controlled to these

registers by the control definitions programmed into the SACU.

8.4

Register Descriptions

8.4.1

Internal Peripheral System Base Address Register (IPSBAR)

The IPSBAR specifies the base address for the 1 Gbyte memory space associated with the on-chip

peripherals. At reset, the base address is loaded with a default location of 0x4000_0000 and marked as

valid (IPSBAR[V]=1). If desired, the address space associated with the internal modules can be moved by

loading a different value into the IPSBAR at a later time.

NOTE

Accessing reserved IPSBAR memory space could result in an unterminated

bus cycle that causes the core to hang. Only a hard reset will allow the core

to recover from this state. Therefore, all bus accesses to IPSBAR space

should fall within a module’s memory map space.

If an address “hits” in overlapping memory regions, the following priority is used to determine what

memory is accessed:

1. IPSBAR

2. RAMBAR

3. Cache

4. SDRAM

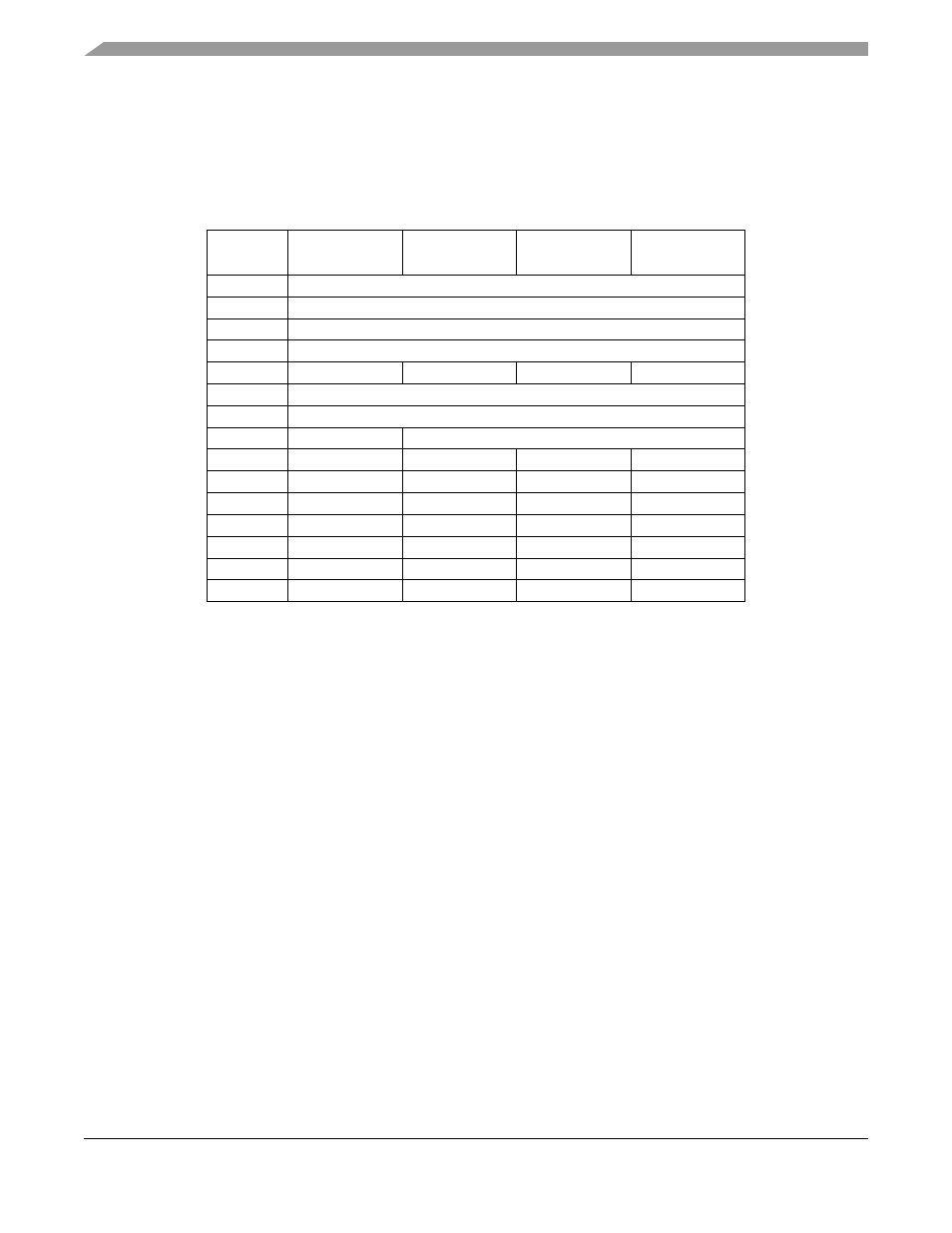

Table 8-1. SCM Register Map

IPSBAR

Offset

[31:24]

[23:16]

[15:8]

[7:0]

0x00_0000

IPSBAR

0x00_0004

—

0x00_0008

RAMBAR

0x00_000C

—

0x00_0010

CRSR

CWCR

LPICR

1

1

."

CWSR

0x00_0018

—

0x00_001C

MPARK

0x00_0020

MPR

—

0x00_0024

PACR0

PACR1

PACR2

PACR3

0x00_0028

PACR4

—

PACR5

PACR6

0x00_002c

PACR7

—

PACR8

—

0x00_0030

GPACR0

GPACR1

—

—

0x00_0034

—

—

—

—

0x00_0038

—

—

—

—

0x00_003C

—

—

—

—

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3