Motorola ColdFire MCF5281 User Manual

Page 166

System Control Module (SCM)

8-14

Freescale Semiconductor

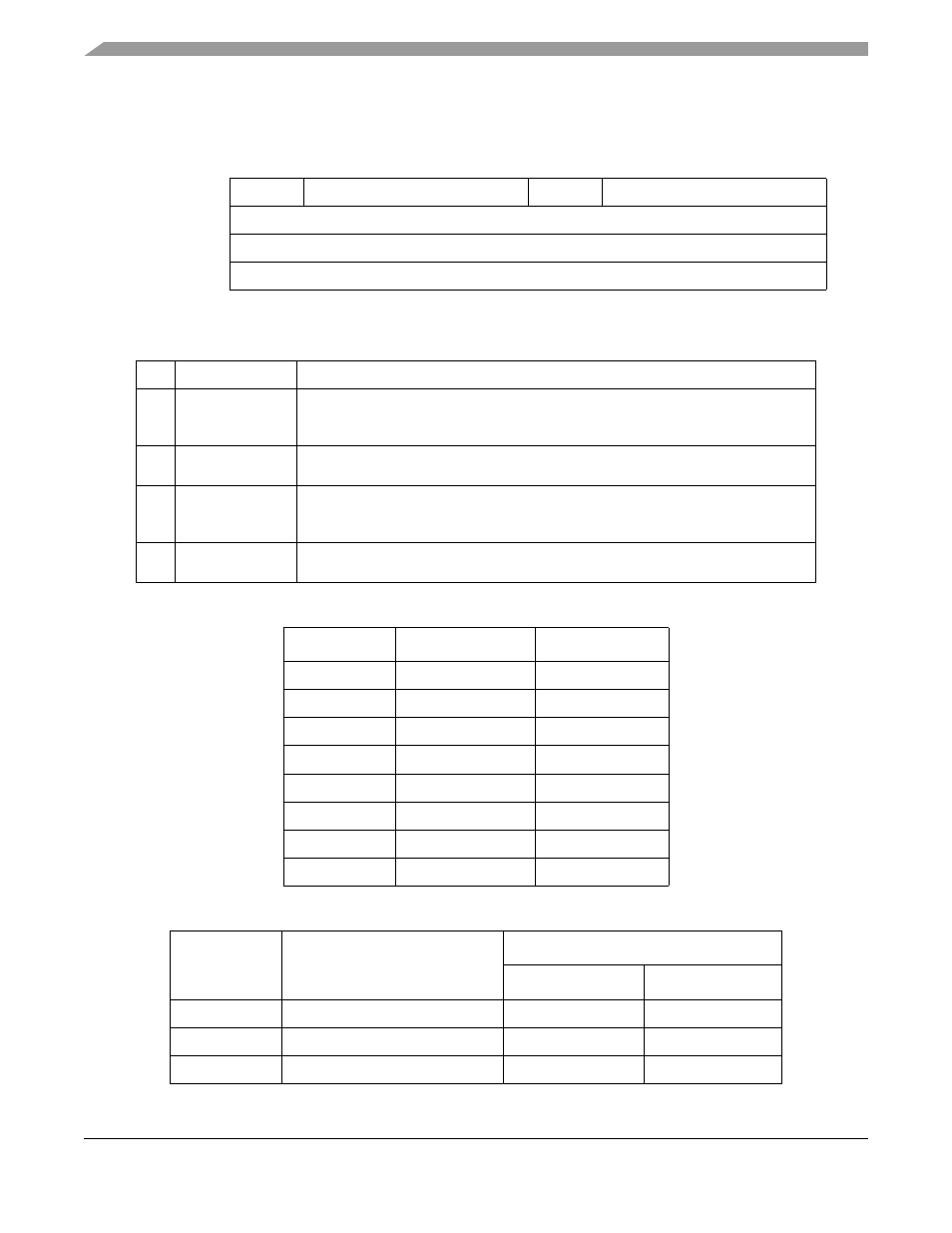

and writes. Each PACR follows the format illustrated in

. For a list of PACRs and the modules

that they control, refer to

7

6

4

3

2

0

Field

LOCK1

ACCESS_CTRL1

LOCK0

ACCESS_CTRL0

Reset

0000_0000

R/W

R/W

Address

IPSBAR + 0x24 + Offset

Figure 8-9. Peripheral Access Control Register (PACRn)

Table 8-9. PACR Field Descriptions

Bits

Name

Description

7

LOCK1

This bit, when set, prevents subsequent writes to ACCESSCTRL1. Any attempted

write to the PACR generates an error termination and the contents of the register are

not affected. Only a system reset clears this flag.

6–4

ACCESS_CTRL1 This 3-bit field defines the access control for the given platform peripheral.

The encodings for this field are shown in

3

LOCK0

This bit, when set, prevents subsequent writes to ACCESSCTRL0. Any attempted

write to the PACR generates an error termination and the contents of the register are

not affected. Only a system reset clears this flag.

2–0

ACCESS_CTRL0 This 3-bit field defines the access control for the given platform peripheral.

The encodings for this field are shown in

Table 8-10. PACR ACCESSCTRL Bit Encodings

Bits

Supervisor Mode

User Mode

000

Read/Write

No Access

001

Read

No Access

010

Read

Read

011

Read

No Access

100

Read/Write

Read/Write

101

Read/Write

Read

110

Read/Write

Read/Write

111

No Access

No Access

Table 8-11. Peripheral Access Control Registers (PACRs)

IPSBAR Offset

Name

Modules Controlled

ACCESS_CTRL1

ACCESS_CTRL0

0x024

PACR0

SCM

SDRAMC

0x025

PACR1

EIM

DMA

0x026

PACR2

UART0

UART1

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3