11 transmit control register (tcr), 11transmit control register (tcr) -17 – Motorola ColdFire MCF5281 User Manual

Page 327

Fast Ethernet Controller (FEC)

Freescale Semiconductor

17-17

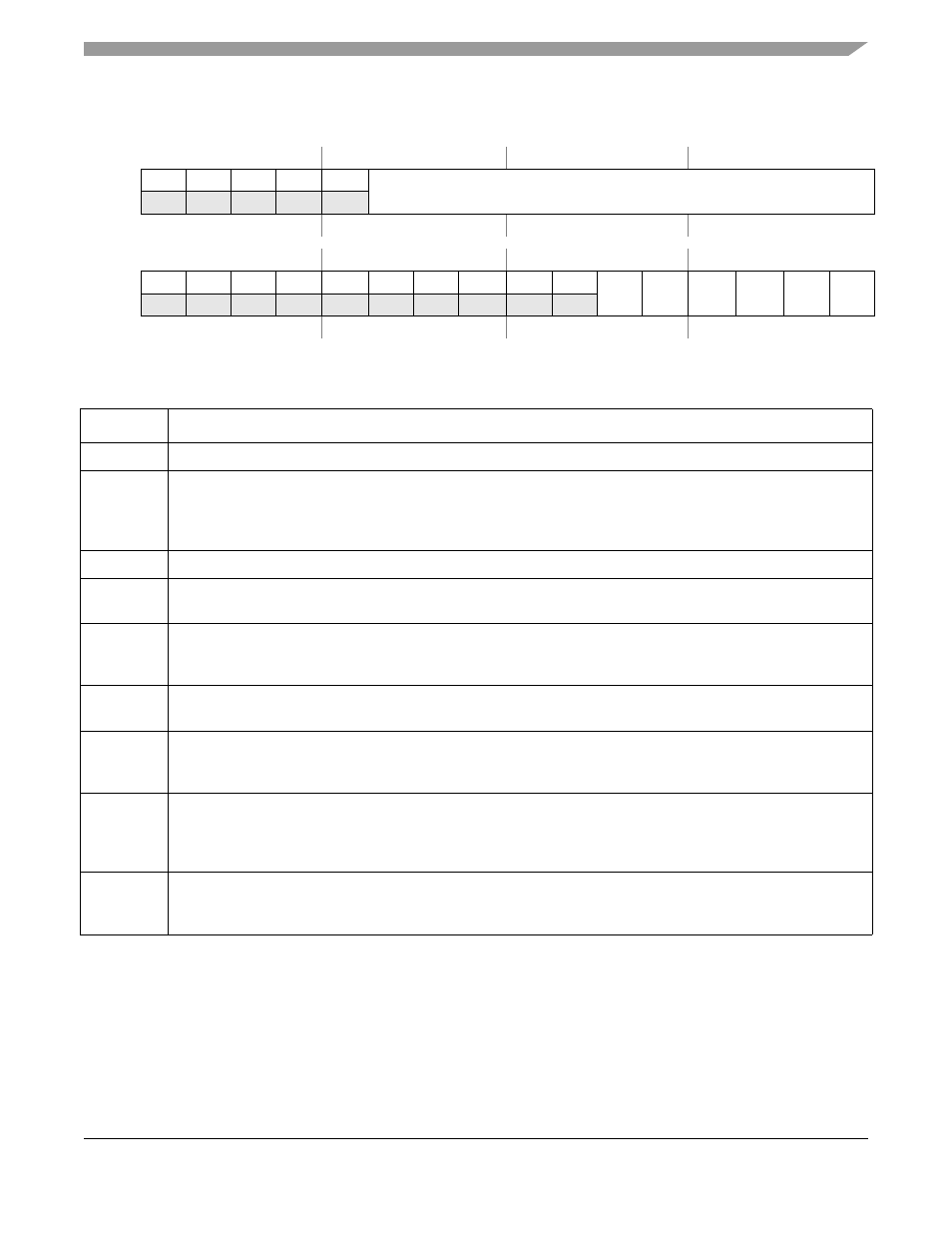

17.4.11 Transmit Control Register (TCR)

TCR is read/write and configures the transmit block. This register is cleared at system reset. Bits 2 and 1

must be modified only when ECR[ETHER_EN] is cleared.

IPSBAR

Offset:

0x1084

Access: User read/write

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

0

0

0

0

0

MAX_FL

W

Reset

0

0

0

0

0

1

0

1

1

1

1

0

1

1

1

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

0

0

FCE

BC_

REJ

PROM

MII_

MODE

DRT LOOP

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

Figure 17-10. Receive Control Register (RCR)

Table 17-14. RCR Field Descriptions

Field

Description

31–27

Reserved, must be cleared.

26–16

MAX_FL

Maximum frame length. Resets to decimal 1518. Length is measured starting at DA and includes the CRC at the

end of the frame. Transmit frames longer than MAX_FL causes the BABT interrupt to occur. Receive frames longer

than MAX_FL causes the BABR interrupt to occur and sets the LG bit in the end of frame receive buffer descriptor.

The recommended default value to be programmed is 1518 or 1522 if VLAN tags are supported.

15–6

Reserved, must be cleared.

5

FCE

Flow control enable. If asserted, the receiver detects PAUSE frames. Upon PAUSE frame detection, the transmitter

stops transmitting data frames for a given duration.

4

BC_REJ

Broadcast frame reject. If asserted, frames with DA (destination address) equal to FFFF_FFFF_FFFF are rejected

unless the PROM bit is set. If BC_REJ and PROM are set, frames with broadcast DA are accepted and the M

(MISS) is set in the receive buffer descriptor.

3

PROM

Promiscuous mode. All frames are accepted regardless of address matching.

2

MII_MODE

Media independent interface mode. Selects the external interface mode for transmit and receive blocks.

0 7-wire mode (used only for serial 10 Mbps)

1 MII mode

1

DRT

Disable receive on transmit.

0 Receive path operates independently of transmit (use for full duplex or to monitor transmit activity in half duplex

mode).

1 Disable reception of frames while transmitting (normally used for half duplex mode).

0

LOOP

Internal loopback. If set, transmitted frames are looped back internal to the device and transmit output signals are

not asserted. The internal bus clock substitutes for the FEC_TXCLK when LOOP is asserted. DRT must be set to

0 when setting LOOP.

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3