5 data breakpoint/mask registers (dbr, dbmr), 5 data breakpoint/mask registers (dbr, dbmr) -12, P. 30-12 – Motorola ColdFire MCF5281 User Manual

Page 630

Debug Support

30-12

Freescale Semiconductor

30.4.5

Data Breakpoint/Mask Registers (DBR, DBMR)

, specifies data patterns used as part of the trigger into debug mode. DBR

bits are masked by setting corresponding DBMR bits, as defined in TDR.

9–8

BTB

Branch target bytes. Defines the number of bytes of branch target address DDATA displays.

00 0 bytes

01 Lower 2 bytes of the target address

10 Lower 3 bytes of the target address

11 Entire 4-byte target address

See

Section 30.3.1, “Begin Execution of Taken Branch (PST = 0x5)

.”

7

—

Reserved, should be cleared.

6

NPL

Non-pipelined mode. Determines whether the core operates in pipelined or mode or not.

0 Pipelined mode

1 Nonpipelined mode. The processor effectively executes one instruction at a time with no overlap.

This adds at least 5 cycles to the execution time of each instruction. Given an average execution

latency of 1.6 cycles/instruction, throughput in non-pipeline mode would be 6.6 cycles/instruction,

approximately 25% or less of pipelined performance.

Regardless of the NPL state, a triggered PC breakpoint is always reported before the triggering

instruction executes. In normal pipeline operation, the occurrence of an address and/or data

breakpoint trigger is imprecise. In non-pipeline mode, triggers are always reported before the next

instruction begins execution and trigger reporting can be considered precise.

5

IPI

Ignore pending interrupts.

1 Core ignores any pending interrupt requests signalled while in single-instruction-step mode.

0 Core services any pending interrupt requests that were signalled while in single-step mode.

4

SSM

Single-step mode. Setting SSM puts the processor in single-step mode.

0 Normal mode.

1 Single-step mode. The processor halts after execution of each instruction. While halted, any BDM

command can be executed. On receipt of the

GO

command, the processor executes the next

instruction and halts again. This process continues until SSM is cleared.

3–0

—

Reserved, should be cleared.

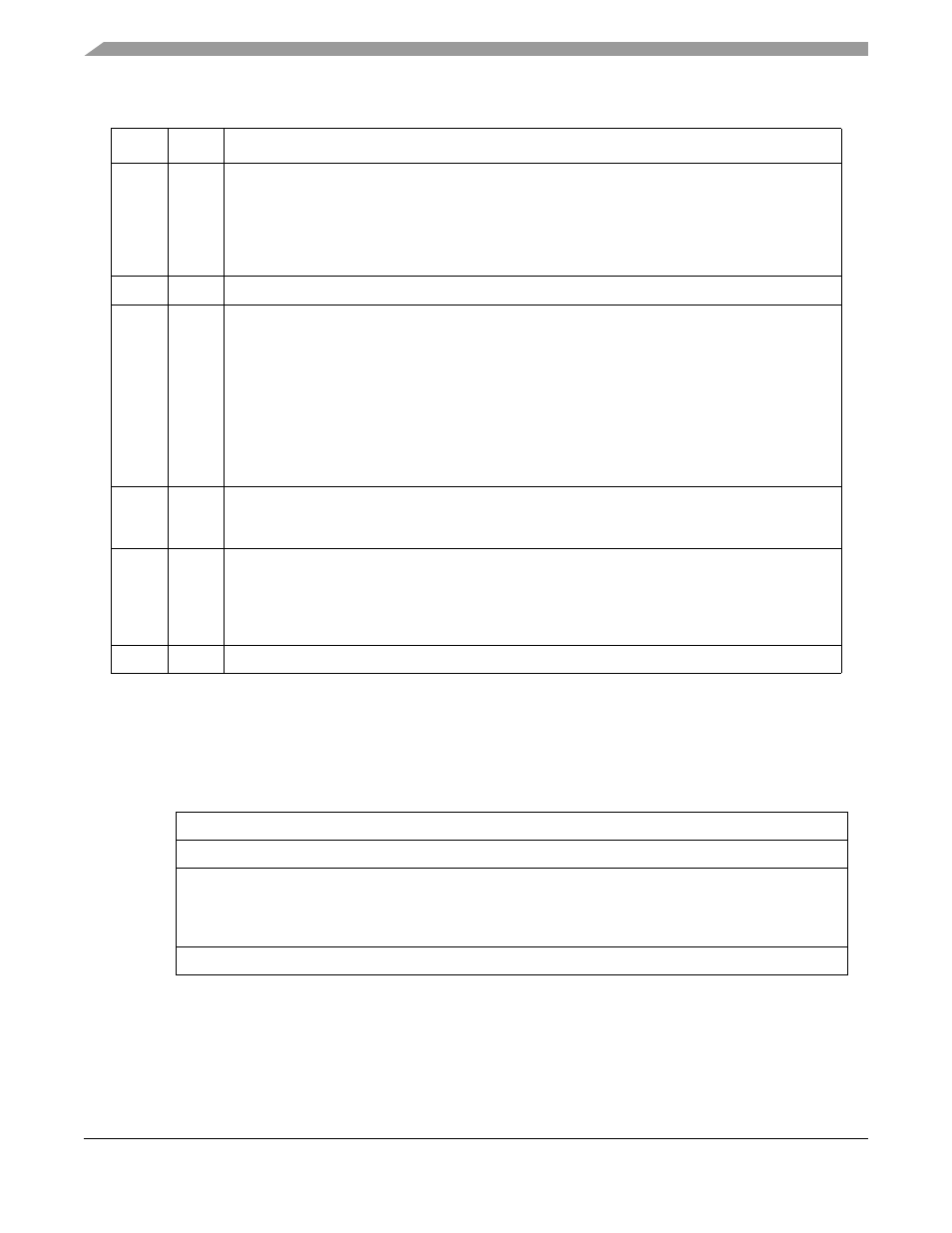

31

0

Field

Data (DBR); Mask (DBMR)

Reset

Uninitialized

R/W DBR is accessible in supervisor mode as debug control register 0x0E, using the WDEBUG instruction and

through the BDM port using the

RDMREG

and

WDMREG

commands.

DBMR is accessible in supervisor mode as debug control register 0x0F,using the WDEBUG instruction and

via the BDM port using the

WDMREG

command.

DRc[4–0]

0x0E (DBR), 0x0F (DBMR)

Figure 30-8. Data Breakpoint/Mask Registers (DBR/DBMR)

Table 30-8. CSR Field Descriptions (continued)

Bit

Name

Description

MCF5282 and MCF5216 ColdFire Microcontroller User’s Manual, Rev. 3